详细阐述了 ADI Subtractive Dither 专利的设计逻辑,AD7124 中的 DITHER 技术正是方式4,并在第一级 Integrator 这里做了巧妙的合并!减轻了对 DAC Matching 的要求

专利下载:ADI_US_8766836_Subtractive_Dither.pdf

¶ 背景

本发明涉及一种改进的 Σ-Δ 调制器。在低输入值或直流(DC)输入下工作的 Σ-Δ 调制器可能会受到闲置音(Tonal Behavior)的影响。例如,输出频谱中可能出现较大的谐波成分(Large Tones),导致信噪比(SNR)下降。抖动(Dither)——一种有意引入的噪声形式——可以被引入以打破这些谐波。然而,引入抖动可能需要回路滤波器具备额外的动态范围(Headroom)。

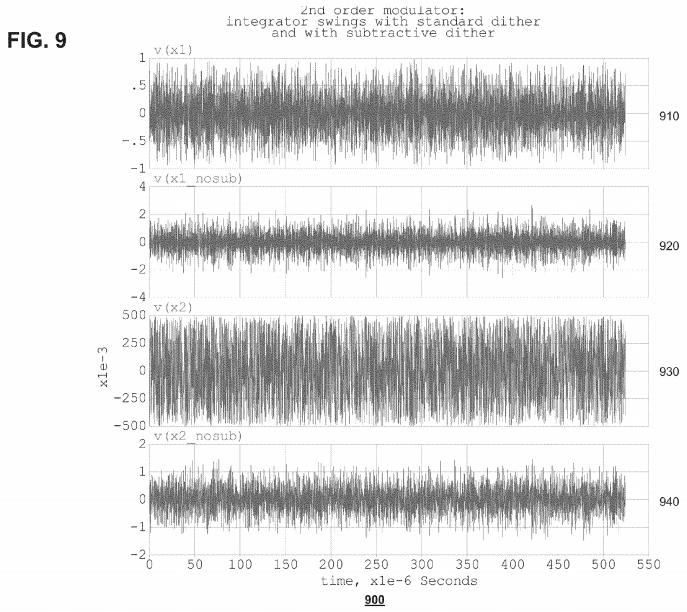

如图 1 所示,在传统的 Σ-Δ 调制器中,抖动信号 110 通常被添加在量化器 130 的前端。通过这种方式,抖动噪声会受到回路滤波器 120 的噪声整形作用,从而使得在调制器 100 输出端的信号带宽内几乎没有抖动功率。但在这种情况下,抖动会被引入反馈回路中,进而要求回路滤波器 120 具备额外的动态范围。例如,在信号传递函数(STF)为单位增益的 Σ-Δ 调制器中,回路滤波器 120 可能仅处理量化误差。如果将抖动直接添加到量化器输入端,抖动会直接叠加在量化误差上,从而增加回路滤波器 120 所需的动态范围。动态范围的增加通常会导致更高的功耗。在低电源电压下,回路滤波器 120 将无法使用高能效的套筒式运算跨导放大器(Telescopic OTA)。因此,为了适应更大的输出摆幅,可能需要使用功耗更高的两级放大器。

¶ 方式一

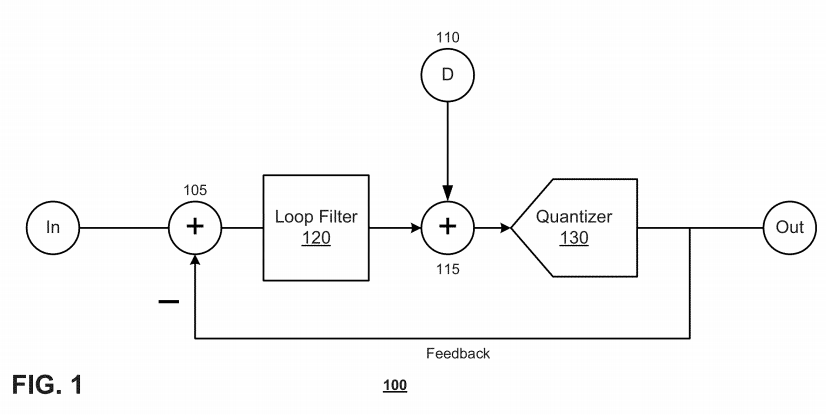

图 2 说明了根据本发明一实施例的一种 Σ-Δ 调制器 200。该 Σ-Δ 调制器 200 可能包括:第一减法器 205、抖动源 210、加法器 215、回路滤波器 220、第二减法器 225、量化器 230 以及设置在反馈路径中的数模转换器(DAC) 240。第一减法器 205 可能具有用于输入信号 IN 和由 DAC 240 提供的反馈信号的输入端,并可能具有一个用于输出代表输入信号 IN 与反馈信号之间差值的信号的输出端。DAC 240 可以将来自调制器 200 的输出信号 OUT 转换为模拟表示,该模拟表示成为进入第一减法器 205 的反馈信号。因此,第一减法器 205 的输出可以代表输入信号 IN 与输出信号 OUT 之间的差值。回路滤波器 220 可以是一个低通滤波器,用于对第一减法器 205 提供的差分信号进行滤波。在另一种实施例中,回路滤波器 220 也可以是带通滤波器或高通滤波器

本来有Tone的信号进入量化器,在 215 这里引入,又在 225 减去,相当于+1又减1,最后的 OUT 看到的数字码,不还是有 Tone 么?--- 答案是没有,可以消除:在传统的数学运算中,。但在电子系统中,量化器(Quantizer) 是一个非线性的“台阶式”函数。

如果输入信号处于量化台阶的某个特定位置(尤其是接近直流 DC 时),量化误差会呈现周期性,产生Tones。在 215 处加入的抖动信号 210 会迫使量化器输入端在多个量化台阶之间快速随机跳变。这意味着量化器产生的“误差”被随机化了,原本集中的能量(Tone)被分散到了整个频谱中;减法器 225 的输出信号 OUT 已经去掉了抖动信号本身,但保留了被抖动随机化后的量化噪声。最终反馈给回路滤波器 220 的信号中,周期性的闲置音已经消失,取而代之的是平滑的噪声频谱

¶ 方式二

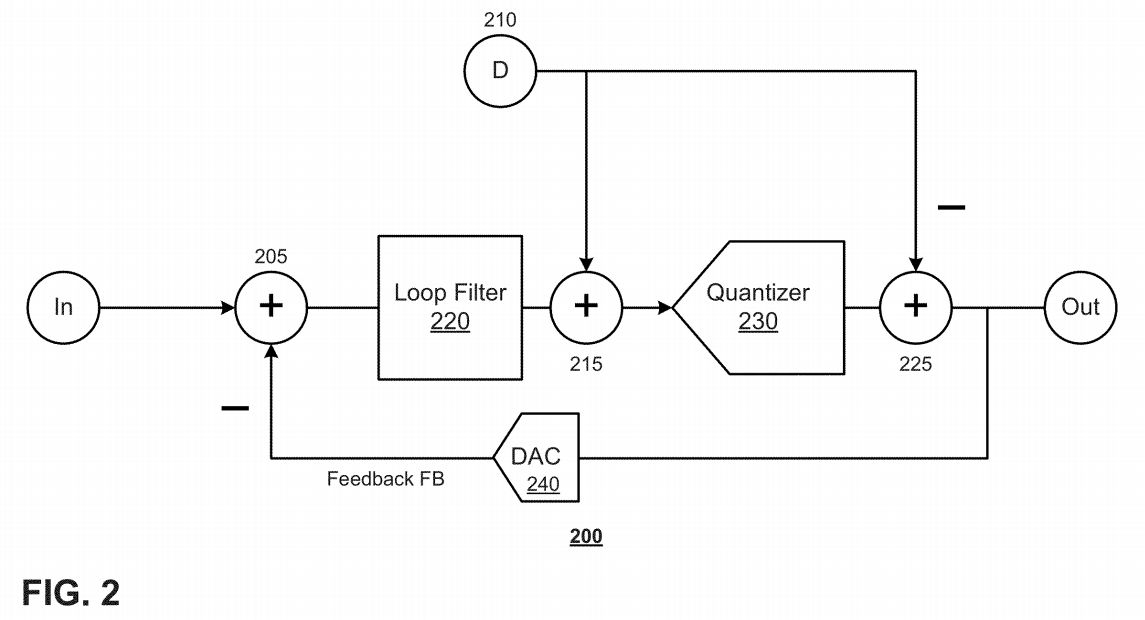

在图 3 所示的实施例中,抖动源 310 可以生成作为数字信号输入调制器的抖动信号。DAC 350 和 360 可以生成抖动信号的模拟表示,并分别输入至减法器 305 和加法器 315。第一减法器 305 的输入包括信号 IN、抖动信号的模拟表示 D 以及由反馈路径中的 DAC 340 生成的反馈信号 FB。第一减法器 305 生成的输出代表输入信号与带有抖动的量化器输出信号 QOUT 之间的差值(例如,)。由于 ,因此实际上 。输出信号 被输入至回路滤波器 320,后者可以是低通、带通或高通滤波器。回路滤波器 320 的输出与抖动信号的模拟表示一同输入至加法器 315。加法器 315 将抖动信号添加到回路滤波器的输出中并输入至量化器 330。量化器 330 生成数字表示并输出至减法器 325。因此,量化器 330 的输出可能包含抖动成分,从而减少闲置音。第二减法器 325 从量化器输出中减去抖动信号 D,有效抵消该成分,并输出信号 OUT。反馈路径中的 DAC 340 从包含抖动成分的量化器 330 输出端获取输入。量化器 330 可以是标量或舍入量化器,位于加法器 315 与减法器 325 之间。

在图 3 所示的实施例中,在回路滤波器 320 后的加法器 315 处引入抖动,并通过减法器 325 及通过 DAC 350 在减法器 305 处移除抖动,可能消除对回路滤波器额外动态范围的需求。由于抖动在到达回路滤波器 320 前已被抵消,因此无需增加动态范围。此外,抖动 DAC 350 用于从反馈回路中移除抖动,使得量化器 330 可以利用抖动打破闲置音,而无需为回路滤波器 320 增加额外的动态范围。

这种方式的优势在于,这个 DITHER 不仅给 Quantizer 加扰,还给 DEM 加扰,代价是 DAC340 的 Dynamic Range 要大一点

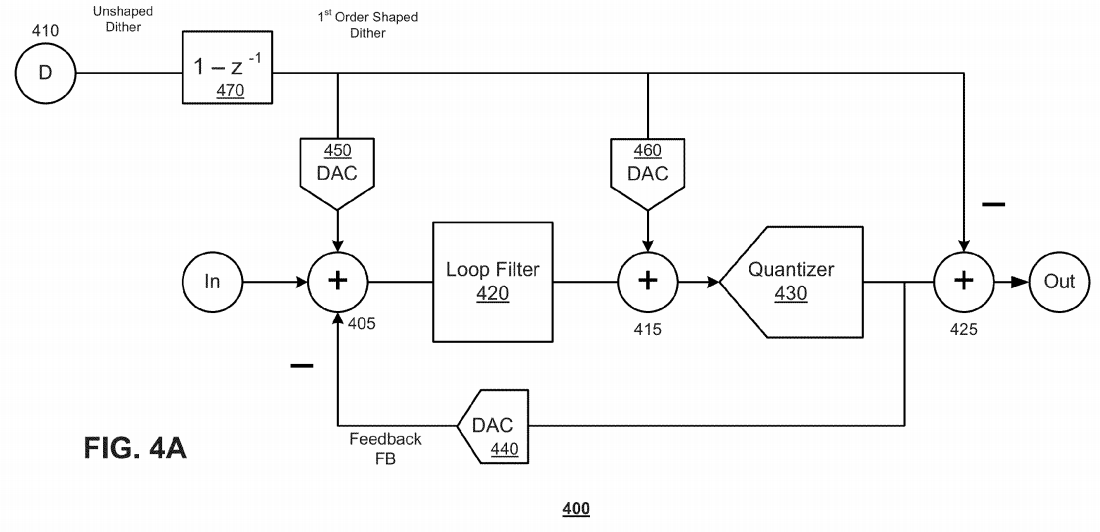

¶ 方式三

对抖动进行整形可以放宽对抖动 DAC(数模转换器)的精度要求。此外,使用一阶整形抖动允许滤波 DAC 在第一级积分器的输出端添加非整形抖动。

由于 450 是在输入端,在这里加入 Dither 就是直接的对信号的干扰,需要非常高的精度才能保证完美抵消,但是这里做了一阶整形,尽可能减少对 Baseband Signal 的影响

¶ 方式四 (AD7124)

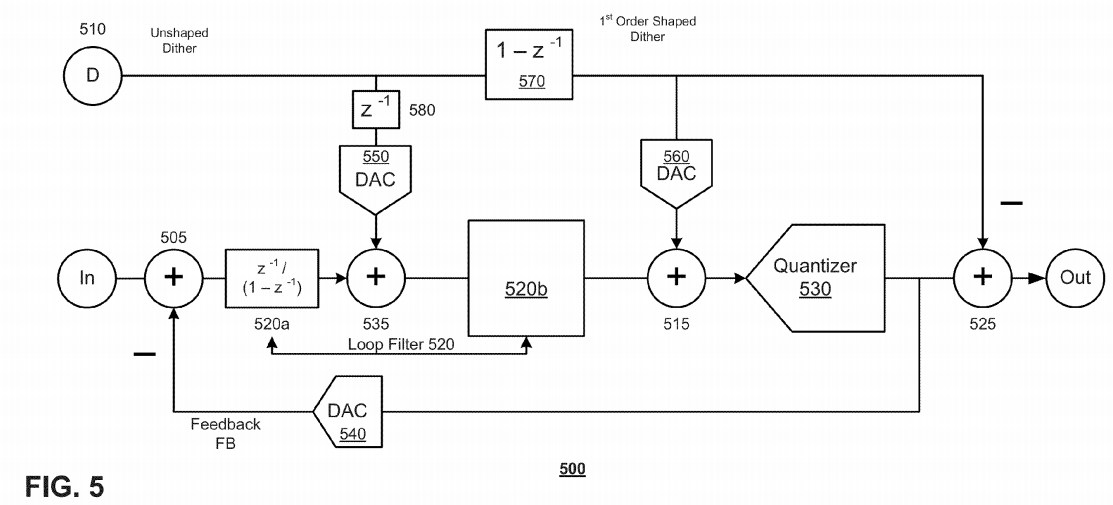

图 5 说明了根据本发明另一实施例的一种 Σ-Δ 调制器 500。该调制器 500 可能包括:第一减法器 505、抖动源 510、第一加法器 515、由第一积分器 520a 和第二部分 520b(可能包括级联积分器或谐振器)组成的回路滤波器、第二减法器 525、量化器 530、第二加法器 535、一系列 DAC 540-560、整形单元 570 和延迟单元 580。调制器 500 在第一减法器 505 输入端接收输入信号 IN,并在第二减法器 525 输出端生成输出信号 OUT。第一减法器 505 生成代表模拟输入信号 IN 与 DAC 540 生成的量化器数字输出模拟表示之间差值的输出信号。

在图 5 所示的实施例中,抖动源 510 生成作为数字信号输入调制器的抖动信号 D。抖动信号 D 最初可能是非整形的,但随后被整形(例如由整形单元 570 根据函数 进行整形)。DAC 550 和 560 分别生成非整形和整形抖动信号的模拟表示,并分别输入至第一加法器 535 和第二加法器 515。在回路滤波器 520a-b 后的加法器 515 处引入整形抖动,并在减法器 525 和通过 DAC 550 在加法器 535 处移除抖动,可能消除对回路滤波器 520a-b 补偿抖动的额外动态范围需求。

在图 5 的实施例中,整形抖动可能在第一积分器输出端而非其输入端被移除。当一阶微分抖动 经由传递函数为 的延迟积分器 520a 处理时,在积分器 520a 的输出端产生抖动分量 (负号由减法器 505 引入)。延迟单元 580 和 DAC 550 可以通过添加抵消抖动分量 来移除该成分。由于抖动在到达回路滤波器 520b 前被抵消,因此 520b 无需额外动态范围。积分器 520a 可能需要额外动态范围来处理抖动,但在实际实现中可能并非如此。此外,DAC 550 的精度要求被放宽,因为任何在积分器 520a 输出端引入的误差,在折合到输入端时都会受到一阶函数的整形。

第一减法器 505 生成输入信号与量化器输出信号 QOUT 的差值()。由于抖动是在回路滤波器后添加并在量化器输出端移除,回路滤波器 520a-b 无需额外动态范围。在开关电容实现中,积分器 520a 和加法器 535 可以合并为公共电路(如图 6 和图 7),仅加法器 535 的输出物理可达,因此积分器 520a 无需额外动态范围。加法器 515 将整形抖动添加到回路滤波器输出并输入量化器 530。第二减法器 525 从量化器输出中减去整形抖动信号 以抵消抖动分量并输出信号 OUT。DAC 540 在反馈路径中生成反馈信号。量化器 530 位于加法器 515 和减法器 525 之间,利用抖动打破闲置音,而无需为回路滤波器 520a-b 增加补偿抖动的动态范围。

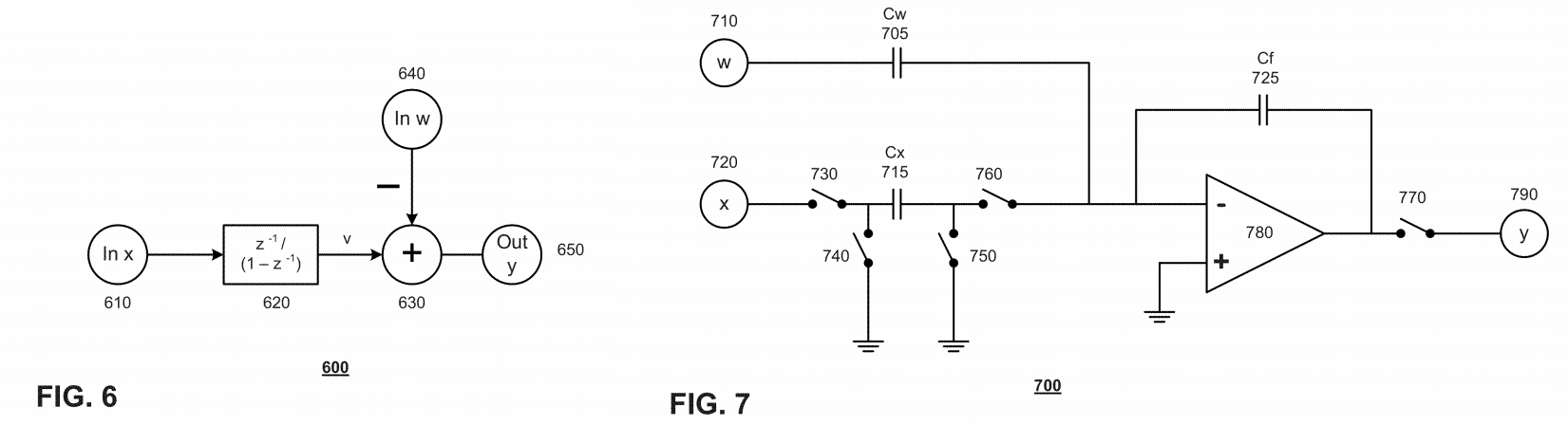

图 6 是根据本发明一实施例的一种组合式积分器/加法器 600。例如,图 5 中的积分器 520a 和加法器 535 可以根据本发明的实施例进行组合。将积分器和加法器组合后仅产生一个合并输出,这可以消除因添加抖动而在积分器中产生额外动态范围的需求。该组合式积分器/加法器 600 可能包括:

如图 6 所示,组合式积分器/加法器 600 可能包括积分器 620 和减法器 630。积分器 620 可以接收输入 x 610。积分器 620 可以应用一个 z 域传递函数,例如 。减法器 630 将输入 w 640 与积分器 620 的输出 v 相结合,以产生输出 y 650。

图 7 是根据本发明一实施例的组合式积分器/加法器的开关电容实现方式。例如,图 5 中的积分器 520a 和加法器 535 可以按照本发明的实施例进行组合,如上述图 6 所示。图 6 的组合式积分器/加法器可以使用开关电容实现方式来构建,例如图 7 所示的那样。使用此类实现方式可以避免在添加抖动时对积分器产生额外动态范围的需求。

在图 7 所示的实施例中,组合式积分器加法器 700 的开关电容实现可能包括开关 730, 740, 750, 760 和 770,以及电容器 Cw 705, Cx 715 和 Cf 725。开关 730, 740, 750, 760 和 770 可以由标准非重叠时钟驱动,其中开关 730, 750 和 770 组成第一组,开关 740 和 760 组成第二组。当第一组接通且第二组断开时,电容器 Cx 715 可以被充电至电压输入 x 720。当第一组断开且第二组保持断开时,输入 x 720 电压可以在 Cx 715 上采样。当第二组接通且第一组断开时,电荷从 Cx 715 转移

715 上的电荷可以转移到 Cf 725 并在之前的电荷之上,从而执行积分功能。如果在 w 输入端施加电压,它将以 为比例出现在输出端。总之,该电路可以实现如下类型的传递函数:

¶ 效果对比

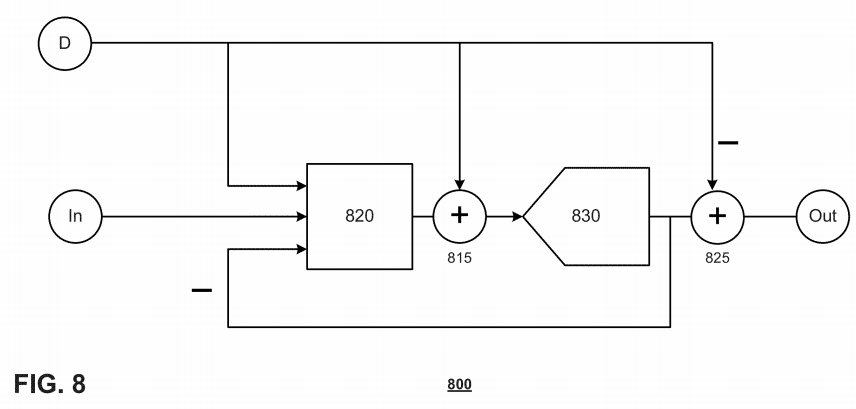

图 8 说明了根据本发明一实施例的一种 Σ-Δ 调制器 800。该 Σ-Δ 调制器 800 可能包括加法器 815、回路滤波器 820、减法器 825 和量化器 830。回路滤波器 820 可以是低通滤波器、带通滤波器或高通滤波器。

抖动源可以向输入端引入抖动信号,该信号可以在所示的任何点引入回路滤波器 820。输入可以直接引入回路滤波器 820,或者可以通过求和节点引入,如上述实施例所示。抖动信号可以通过加法器 815 应用于回路滤波器 820 的输出端。在一实施例中,抖动信号可以被整形,如上文关于图 4 和图 5 所讨论的那样。

量化器 830 可以对输入信号进行量化并将其输出至减法器 825。减法器 825 可以从量化器 830 的输出中减去该抖动信号。在一实施例中,量化器 830 可以是一个标量或舍入量化器。减法器 825 的输出可作为系统的输出信号 OUT 从系统 800 中输出。此外,反馈回路可以将量化器 830 的输出引入回路滤波器 820。

如上文所述,抖动信号可以在加法器 815 处被引入,并在减法器 825 处被移除。通过这种方式,量化器 830 可以利用抖动来打破可能由于量化器 830 产生的量化噪声而导致的潜在闲置音行为。同时,通过在回路滤波器 820 中移除抖动,不需要在回路滤波器 820 内提供额外的动态范围来容纳该抖动信号。因此,通过在回路滤波器 820 之后、量化器 830 之前引入抖动信号,并且进一步在回路滤波器 820 中移除抖动信号,图 8 的实施例为通常与添加抖动相关的动态范围问题提供了一种直接且低成本的解决方案。

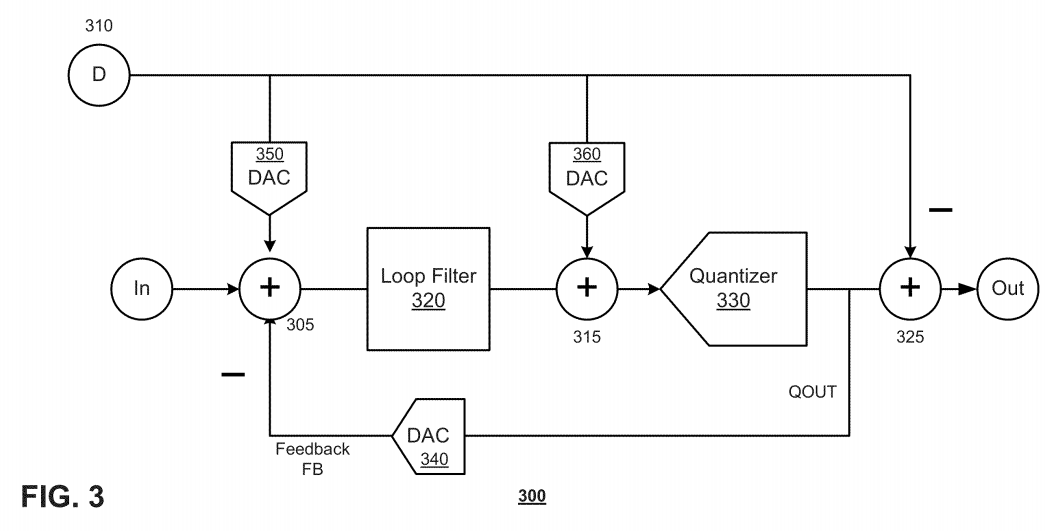

图 9 说明了一系列代表在使用标准抖动和减法式抖动情况下的积分器摆幅图表。这些图表代表了使用本发明实施例的示例性结果。如曲线图 910 和 930 所示,使用减法式抖动技术可以显著减小摆幅。曲线图 920 和 940 代表了不使用减法式抖动技术时的摆幅。如图所示,使用减法式抖动时摆幅可以被显著减小。