本文对CDAC电容本身的相关问题进行一些分析,涉及到

¶ Mismatch and Nonlinearity

在CDAC

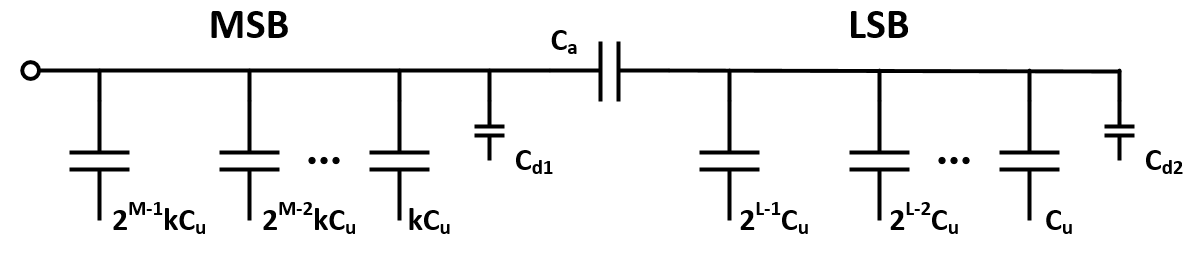

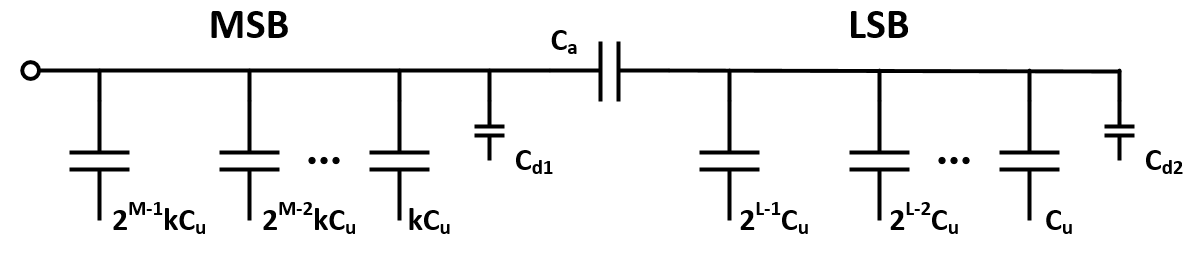

当SAR的精度提高时,CDAC的位数将不可避免地提高,为了保证LSB电容的匹配精度,通常有一个最小的 Cu,而最高位比如传统的下极板采样(Switching-Strategy-and-Power#2.2 Traditional)的最高位将会是 2L−1Cu,考虑差分两端的总电容将会是2L+1Cu,这样的面积以及对VREF-Driver的驱动能力要求都是非常夸张的。

通过桥接电容的方式,可以有效地减少高位电容的个数。比如对于 L bit 的CDAC,当L/2 bit 的电容时,我们通过一个串联电容 Ca 将这些电容等效为一个 Cu 后,L/2+1 bit 就又可以回到原点 Cu 开始递增了

但是,照着这样的思路,会发现

CuCaL=10Ca=Ca+2LCuCa⋅2LCu=2L−12LCu=10231024Cu

在实际设计中,几乎不可能精确实现一个这样的分数电容,迫切需要对桥接电容进行整数化处理。

重新思考对Segmented-CDAC的根本诉求,并不是让LSB总电容和桥接电容的串联电容等于MSB的最高低位电容,根本诉求是:MSB最低位变化在输出的 ΔV1 和LSB最高位比变化产生的 ΔV2 应该满足 ΔV1=2ΔV2 的关系,才能保证CDAC的基本功能。所以接下来的思路,就是分别写出 ΔV1,2的表达式

利用电荷加权和逐层替换,可以很容易地写出 ΔV1,2 ,在此之前可以先写出 “分总” 电容的表达式

CLtCMt=(2L−1)Cu+Cd1=(2M−1)kCu+Cd2

然后 ΔV1,2 的表达式如下

ΔV1ΔV2=CMt+Ca+CLtCaCLtkCu⋅Vref=CMt(Ca+CLt)+CaCLtkCu(Ca+CLt)⋅Vref=CLt2L−1Cu⋅CMt+Ca+CLtCaCLtCa+CLtCaCLt=CMt(Ca+CLt)+CaCLt2L−1CuCa⋅Vref

令 ΔV1=2ΔV2,可以得到

kCu(Ca+CLt)kCu(Ca+CLt)kCuCLtCuCaCuCa=2⋅2L−1CuCa=2LCuCa=(2L−k)CuCa=2L−kk⋅CuCLt=2L−kk⋅Cu(2L−1)Cu+Cd2

接下来,我们的思路是,遍历 {k,CuCa}∈Integers ,去验证CLt 和 Cd2 同时满足 是 Cu 的整数倍

| k |

Ca/Cu |

|

C_ |

C_ |

| 1 |

1 |

⇒ |

(0+1)\times2^{L-1}C_ |

0\times2^{L-1}C_ |

| 1 |

2 |

⇒ |

(1+1)\cdot2^{L-1}C_ |

1\times2^{L-1}C_ |

| 1 |

3 |

⇒ |

(2+1)\cdot2^{L-1}C_ |

2\times2^{L-1}C_ |

| 1 |

4 |

⇒ |

(3+1)\cdot2^{L-1}C_ |

3\times2^{L-1}C_ |

| 1 |

N+1 |

⇒ |

(N+1)\cdot2^{L-1}C_ |

N\times2^{L-1}C_ |

上面总结出了一套方式,如果是 k=2 的话,则有

| k |

Ca/Cu |

|

C_ |

C_ |

| 2 |

4 |

⇒ |

(2L+1−4)Cu |

(2L−3)Cu |

| 2 |

5 |

⇒ |

(25⋅2L−5)Cu |

(3⋅2L−1−4)Cu |

上述这个过程,工具中现有的函数没智能到直接得到约化结果,我们可以写一个迭代查找脚本实现这一点

ClearAll["Global`*"]

k = 2; cu = 1;

expr = k/(2^L - k)*((2^L - 1)*cu + cd2)/cu;

For[result = 1, result <= 6, result++,

{

cd2Solve = Solve[expr == result, cd2];

(*Mathematica正整数判定无法判断非显式表达式,L\[GreaterEqual]2*)

cd2SolveJudge = cd2Solve[[1, 1, 2]] /. L -> 2 // FullSimplify;

(*Positive and Integer Judgement*)

If[IntegerQ[cd2SolveJudge] && Positive[cd2SolveJudge],

Print["k=", k, " ca/cu=", result, " cd2=", cd2Solve[[1, 1, 2]]]]

}]

在桥接电容整数化的分析过程中,发现对MSB的寄生电容 Cd1 没有要求。再次观察 ΔV1 和 ΔV2 的表达式

ΔV1ΔV2=CMt(Ca+CLt)+CaCLtkCu(Ca+CLt)⋅Vref=CMt(Ca+CLt)+CaCLt2L−1CuCa⋅Vref

发现包含 Cd1 的 CMt,会同时且仅出现在高位和低位分母上,那这样会只引入一个增益误差;而包含 Cd2 的 CLt 在高位和低位的表现不一样,发生区间切换时会导致DNL问题

引入冗余的目的是纠错和提速,出错的原因如下:

- CDAC建立精度问题,VREF-Driver的驱动能力,已经采样开关电容的RC

- 比较器的噪声,动态比较器噪声较差

- 电源/地网络寄生,主要是电阻和电感,造成比较错误

通过提高对比较错误的免疫的能力,从而降低对VREF-Driver的功耗和驱动时间,放宽对比较器最小分辨电压的要求。