¶ 1 Introduction

本文对比了下极板采样 (Bottom-Plane-Sampling) 和上极板采样 (Top-Plane-Sampling) 对 VREF 的功耗需求,给出了不同开关切换策略的"深层"思考,同时也针对一些特定情况给出了电荷计算直观方法,最后给出了程序化 Mathematica 代码去实现高分辨率CDAC的能量计算。

通常我们认为高精度用下极板采样,高速用上极板采样

- 上极板采样:缺点是 Input Related Charge Injection,影响线性度,大约10bit;优势是结构简单,且与节省功耗的开关策略高度适配;

- 下级版采样:结构复杂至少需要3个开关和控制信号;优势是可以通过时序仅有上极板侧开关的的固定失调。

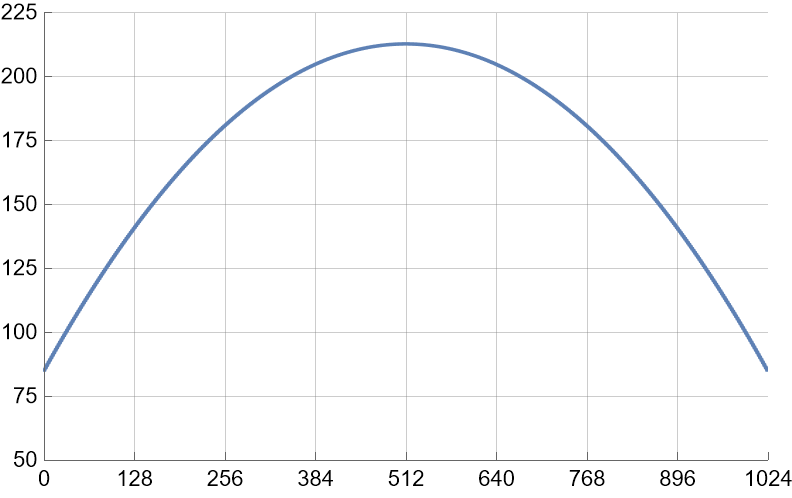

下表总结了本文中对比的几种开关切换策略,使用不同的开关策略会影响比较器输入共模和功耗,同时也看到上极板采样有非常大的功耗优势,节省VREF驱动能量的的动机是因为VREF-Driver可能会成为限制系统性能的瓶颈。

| Strategy | Caps | 10-Bit Average Energy | CMP-Input-VCM |

|---|---|---|---|

| BPS-Traditional | 2 × 2^N | 1363.33 | 维持不变 |

| BPS-Sanyal | 2 × 2^(N-1) | 先增后减 | |

| BPS-VCM-Based | 2 × 2^(N-1) | 维持不变 | |

| TPS-Monotonic | 2 × 2^(N-1) | 255.5 | 单调递减 |

| TPS-Sanyal | 2 × 2^(N-1) | 127.5 | 先增后减整体不变 |

| TPS-VCM-Based | 2 × 2^(N-1) | 170.167 | 维持不变 |

¶ 2 Bottom-Plane-Sampling

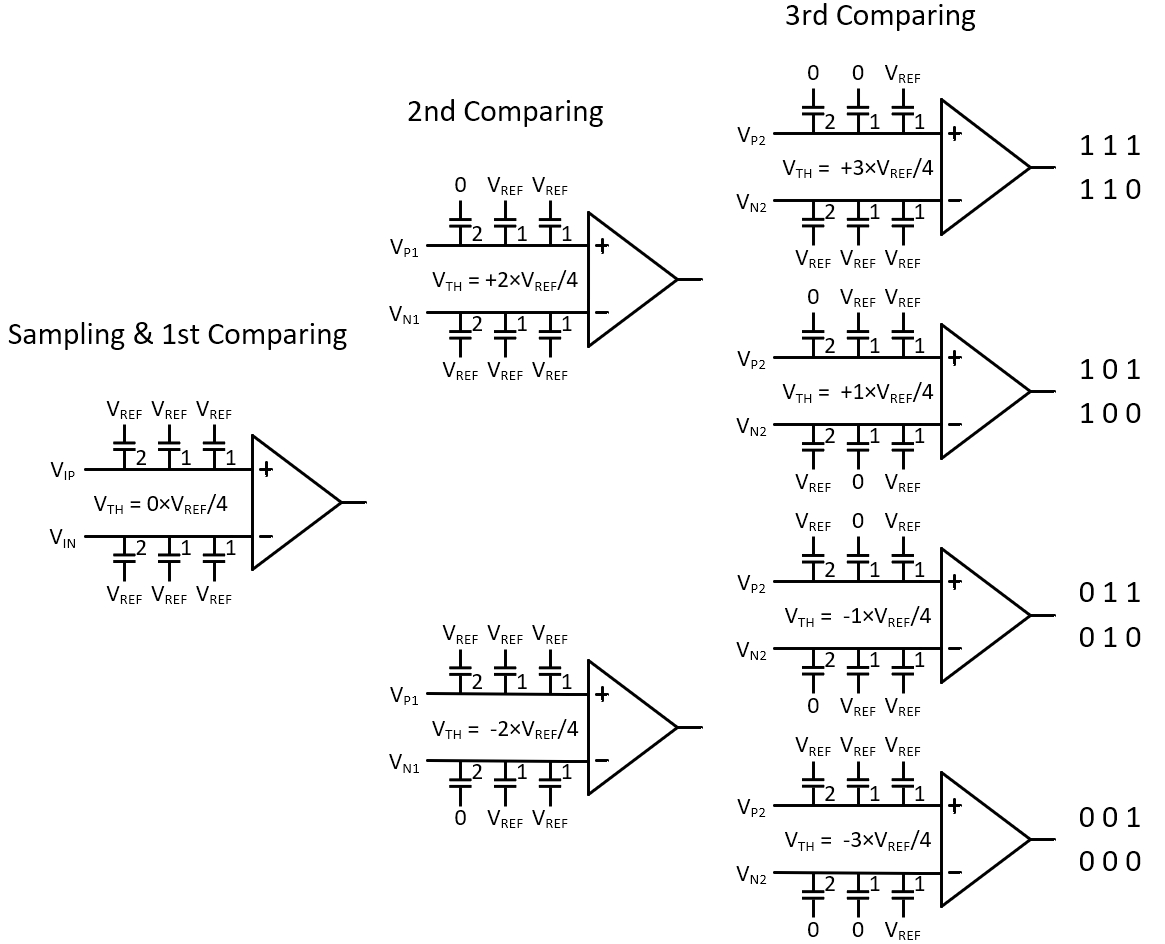

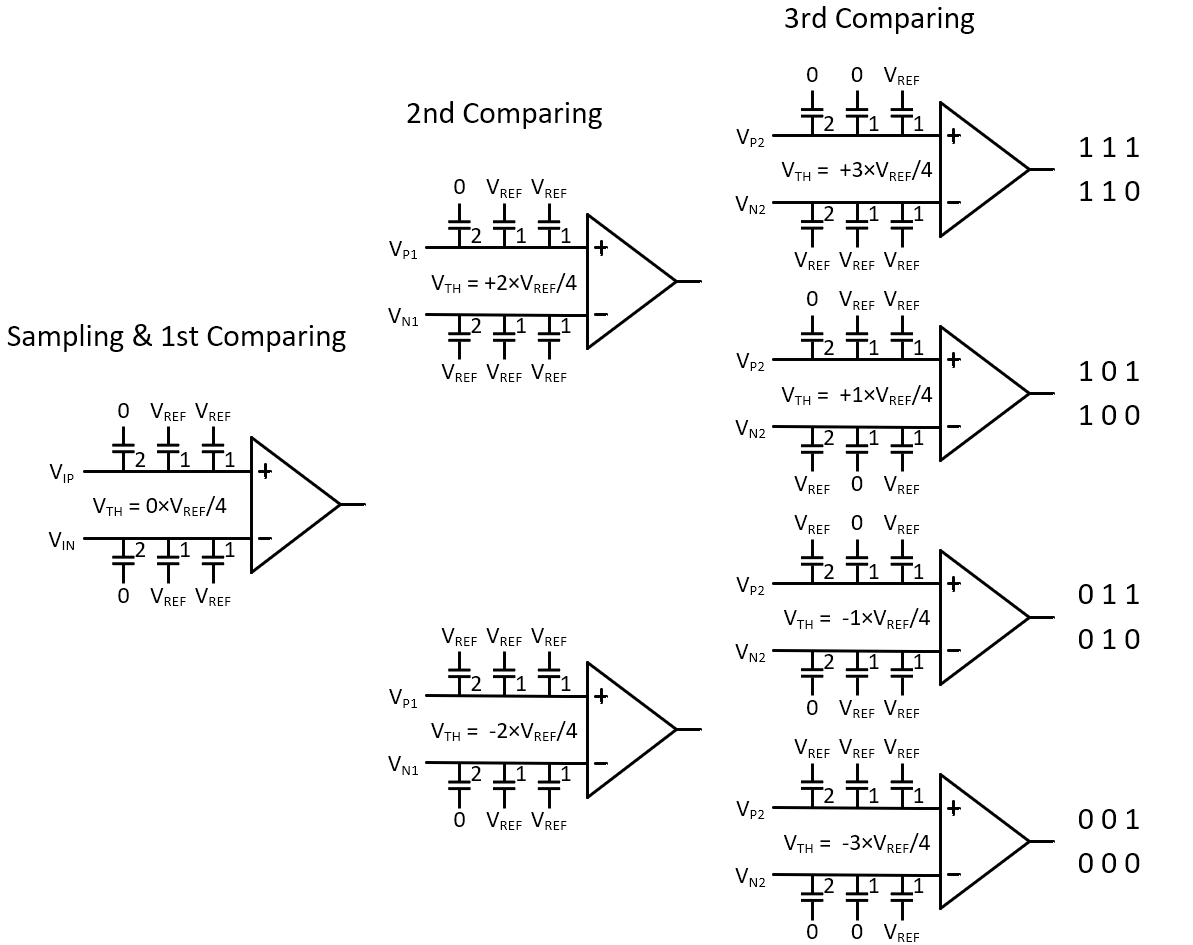

¶ 2.1 Understanding BPS-Operation

下极板采样,直观理解是,采样阶段下极板采样完信号后,需要用CDAC去拟合输入信号。

- 对于正向输入端,输入的增量,等于下极板的 本次-上次,由于下极板本次是VCDAC,上次是V(IP,IN),所以每次比较的结果是VCDAC-V(IP,IN)。如果比较结果小于0,认为当前CDAC返回的等效VCDAC不够,需要继续补更多,所以正向输入端的CDAC反馈值需要继续提高;

- 对于反向输入端,正向输入端的增量,等效于反相输入端减量。所以如果比较结果小于0,认为VCDAC不够,需要补更多,所以反向输入端的CDAC反馈值需要继续减小。

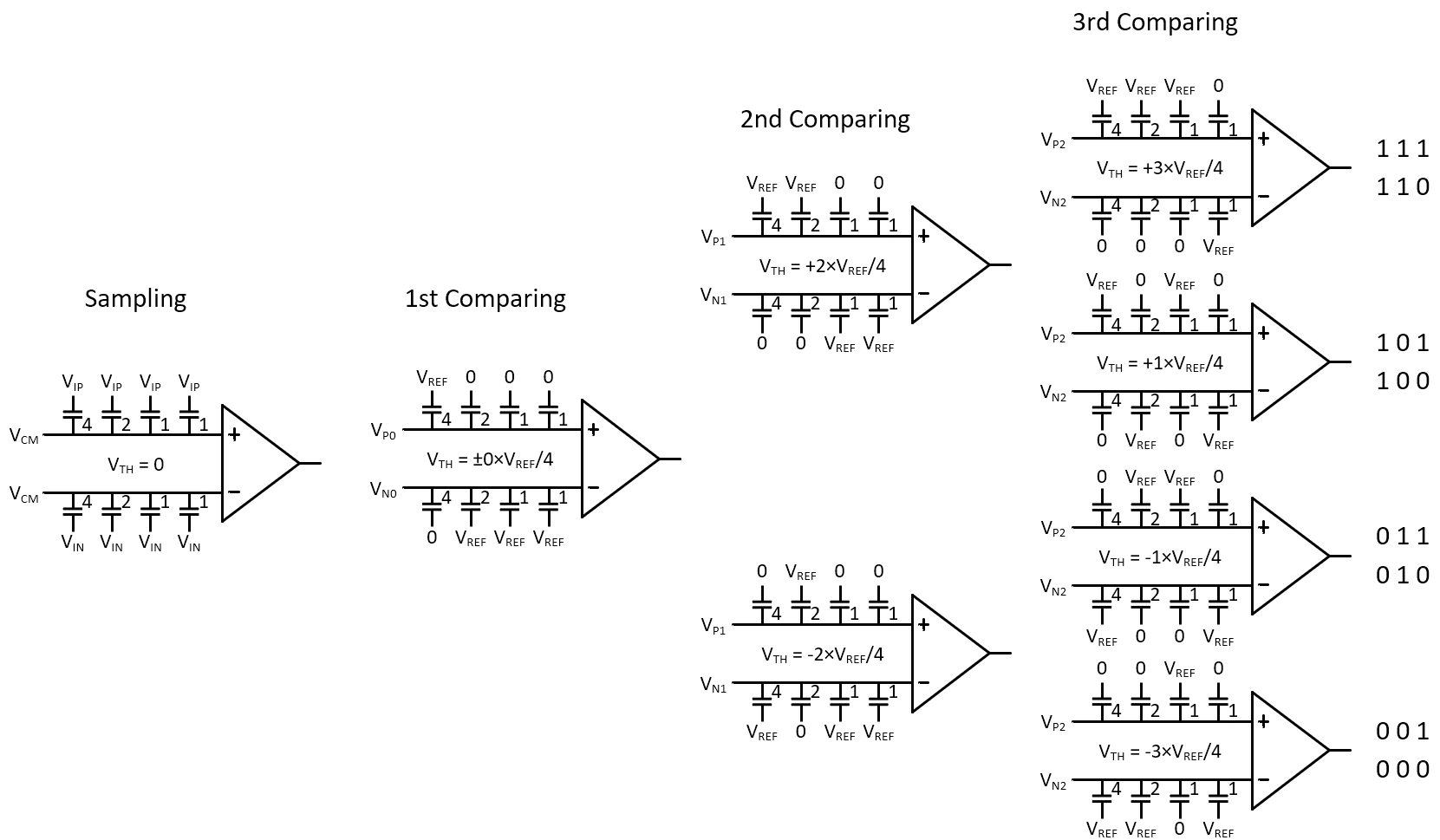

下图所示的过程,比较结果为负,则向上走一格。反之则向下走一格:

¶ 2.2 Traditional

¶ 2.2.1 Illustration

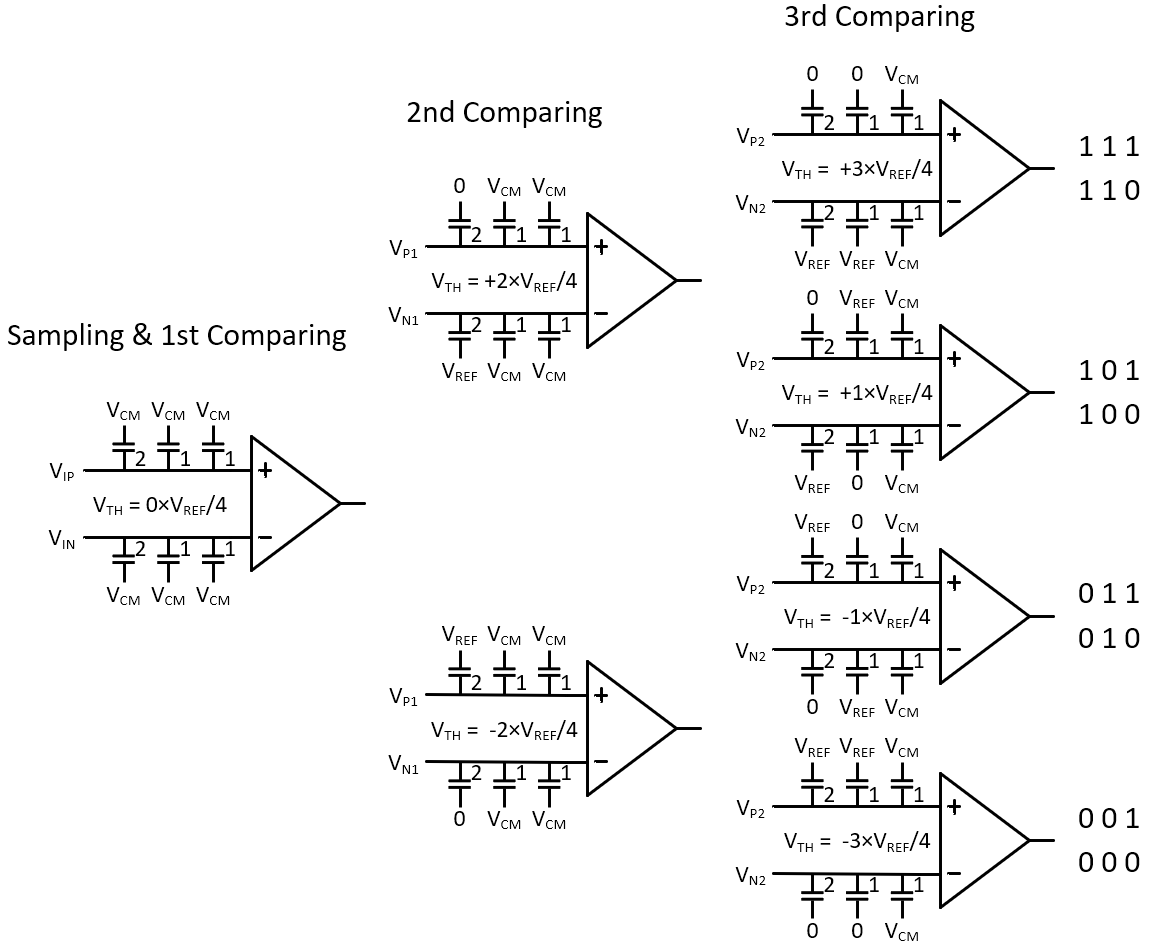

- 第一次采样:上极板=VCM (通常时VDD/2),下极板=VIP/VIN;

- 第一次比较:MSB猜1,上极板=1000,下极板=0111(全差分,可以认为上极板的数据就是ADC的结果;下极板永远是上极板的反);如果 CMP=0,则保留上极板的1和下极板的0;如果CMP=1,上极板反转为0,下极板反转为1;

- 第二次比较:次MSB猜1,上极板=x100,下极板=x011(认为x已经比较出结果了),同理,如果CMP=0,保留上极板的1和下极板的0;如果CMP=1,反转上下极板的电压;

- 第三次比较:次次MSB猜1,上极板=xx10,下极板=xx01...

- ...

¶ 2.2.2 个人思考

需要额外指出,传统的BPS单侧需要 个电容理解如下,例如对于3bit的CDAC

- 相比TPS的首次MSB位 (直接比较VIP和VIN即VTH=0) 无需置位的特点,BPS首次MSB是需要置位的

- 置位成VTH=0之后,要实现VTH=+3/+2/+1,那么必然还是需要2C:1C:1C个电容的,第一个2C用于VTH=+2,第二个1C用于+1实现VTH=+3,负向输入端的第二个1C用于-1实现VTH=+1,第三个1C用于补位否则Full-Scale就不是 ,LSB也不是 而是

- 为了置位VTH=0,需要上下极板给同样的电压,这样才能把下极板的输入信号反推到上极板去实现VIP和VIN的直接比较

- 假设首次给的等效电压是,那么,最简单的是这里或者,那么这个置位过程将不会有能量消耗

- 但是由于,那么,为了保证这个值仍然在电源轨道之内,最好的方式就是令

- 可以观察到,只要 ,,第一次比较时的输入电压一定不会在电源轨之外,而 , 的这个条件是非常容易满足的。

- 为了实现 ,简单的办法就是加权平均,即一半电容接,一半电容接

- 此时最简单的做法是,上面的4个电容中,2个接 ,另外两个接 ,将来为了增加 VTH 时,只能从正负端二选1实现VTH的变化,因为增加VTH意味着正端下极板的电压永远需要增加,负端下极板的电压永远需要下降

- 当需要VTH上升时,正向输入端首次置位时接 的已经升无可升只能依赖与反向输入端的下降等效实现;负向输入端首次置位时接 的已经降无可降只能依赖于正向输入端的上升实现等效

- 问题来了,当前最高位的一个状态已经用于置为VTH=0了,那么接下来的±2如何实现呢:如果是 011-011这种情况,首次比较结果大于0后111-011实现+2;比较结果小于0后011-111实现-2

- 这种每次只能从正负2选1的方式,会导致比较器的输入共模共模电压一直在变化

- 另一种做法就是图示这种,通过额外增加4个电容的方式,除了首次置位将比较器的共模从变化为,之后CDAC的置位过程都是全差分(一边升高,一边降低),这样比较器的输入共模会维持不变。采样共模和比较共模不一致没有关系,比较器从第一次采样到最后一次采样,共模始终是一致的。

¶ 2.2.3 CDAC第1次置位能量

【基本计算方法】

利用电荷守恒求出浮空点电压

那么接VREF需要提供的电荷是

同理,下极板需要的提供的电荷同样也是

这里给出能量与电荷的关系:

所以采样到首次置为需要的能量为

【串联电容计算方法】

将所有的电容看成一个整体,我们不关心内部即浮空节点的电荷、电位,因为其不会改变。我们将所有的8C看作一个整体,那么这是一个4C串联(2C+C+C)电容,初始状态这个2C电容的上下两端的电位差是 ,置为之后的电位差是 ,那么显然可以得到

负端的同样可以看成是一个(2C+C+C)串联4C的电容,初始状态这个2C电容的上下两端的电位差是 ,置为之后的电位差是 ,同样可以得到

这样总的能量同样可以得到

¶ 2.2.4 CDAC第2次置位能量

观察如果第一次比较结果为1,观察正向输入端的情况。

如果使用传统/串联的方式,都比较繁琐。我们可以使用电荷加权的方式去计算。2C的电容电压从0变化到VREF,一共有8个C,那么浮空点电压的增量为

整个系统的电荷流入和流出守恒,VREF流入的电荷,一部分通过高位的4C回收了,真正给出去的是从GND的2C流走的,因此提供的电荷是

同理,负向输入端,VREF -> GND流入的电荷(GND-VREF=负电荷),需要依靠VREF给回来(正电荷)

所以总的能量为

¶ 2.2.5 CDAC第N次置位能量

如果CDAC变化前后,直是选择接VREF或者GND,那么一个高效算法是

0变1的电荷 = VREF的电压 × 变化位电容 ÷ 总电容 × 接0的电容之和

之所以是 “接0的电容之和” 是因为这部分是确定需要从VREF-Diver提供的,原有接VREF的电容,由于ΔV是负的,可以再被VREF-Driver回收;

1变0的电荷 = VREF的电压 × 变化位电容 ÷ 总电容 × 接1的电容之和

之所以是 “接1的电容之和” 是因为这部分是确定需要从GND-BUS抽走的,原有接GND的电容,由于ΔV是真的,可以再被GND-BUS回收;从GND-BUF抽走的需要从VREF-Diver提供,否则不满足 Kirchhoff Current Law.

如果CDAC除了接VRREF/0,还有可能接VIP/VIN/VCM的话,为了推导更一般的结论,计算需要分两步走

上极板的电压变化 = Σ(下极板的电压变化 × 电容) ÷ 总电容

首先计算出浮空极板的电压变化,注意我们认为 变化总是 = 当前时刻 - 上一时刻

VREF-Driver提供的电荷 = Σ((下极板电压变化 - 上极板电压变化) ×当前下极板接VREF的电容))

需要注意的是,虽然系统的变化是下极板改接VREF的电容位造成的,但是我们仍然需要考虑那些下极板没改变一直接VREF的电容位,虽然他们的下极板没有发生变化,但是其上极板发生了变化,会被迫成为电荷回收通路;

N bit在该开关策略下电容需要置位N-1次,例如对于4bit

1111:xxxx -> 1000 -> 1100 -> 1110 -> 1111

1011:xxxx -> 1000 -> 1100 -> 1010 -> 1011

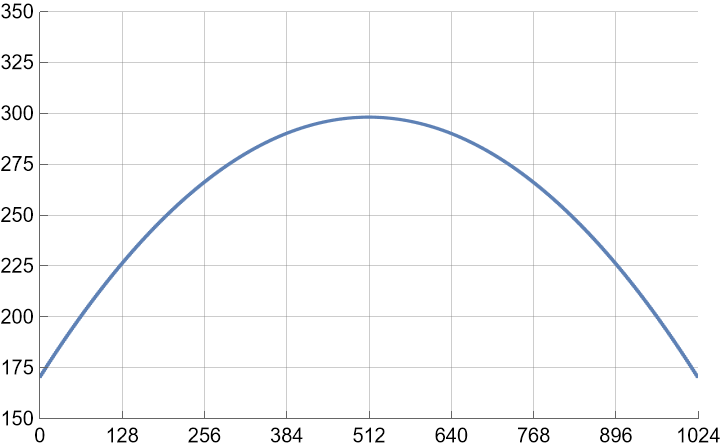

¶ 2.2.6 Mathematic

IMG-Switching-Strategy-and-Power-20241110081004994.nb

Average Energy=1363.33

¶ 2.3 Nonsense-Invention

在尝试理解 traditional bps switching strategy 的过程,突然悟到了两种更省电容阵列和功耗的电容切换方案。但是写完后,发现这个正是BPS版本的Sanyal和VCM-Based。所以称之为无意义的发明创造。

¶ 2.3.1 Sanyal

这种方案,还是通过一半电容VREF,一半电容GND的方式实现下极板VREF/2的首次置位,之后通过单端置位的方式,逐渐改变CDAC的反馈值逐次逼近。

回头思考 traditional 为什么能实现每次电容置位时上正负端同时变化?这是因为每次置位过程中,当前位的电容总是单方向变化,也就是只会让CDAC的等效VCDAC增加,是单方向变化的,如果每次变化都是单方向的,我们是可以做到全差分变化的。那么如果每次变化只能单方向,我们如何从+0阈值切换到-2阈值呢?方式就是要去改变之前位的极性,将高位的+0直接切换为-4,这样-4+2就可以得到-2的阈值了。

¶ 2.3.2 VCM-Based

由于电容置位过程,正负向输入端不能不能一增一减,导致共模会变化。如果引入第三个电压位 VCM=(VREF+GND)/2 就能解决这个问题

¶ 3 Top-Plane-Sampling

¶ 3.1 Understanding TPS-Operation

上极板采样,直观理解是,采样阶段上极板采样完信号后,需要用CDAC去抵消输入信号。

- 每次比较的结果实际上 V(IP,IN)+VCDAC,如果比较结果大于1,说明VCDAC不够负,需要更负一点;

- 正向输入端的下极板通过减小电压实现更负;负向输入端的下极板通过增加电压来实现更负。

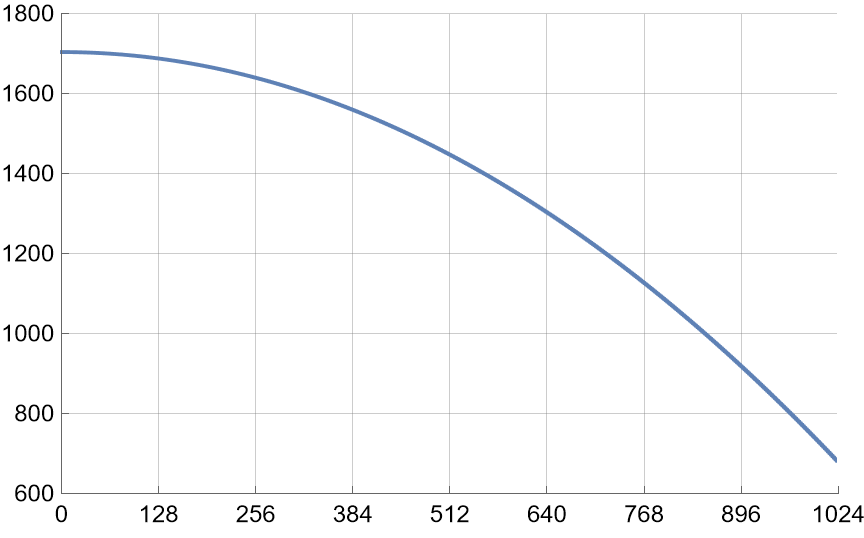

下面的图中,每次比较结果为正,则向上走一格,反之则向下走一格

¶ 3.2 Monotonic

¶ 3.2.1 Illustration

由于上极板采样,且CDAC的下极板初值只有两种状态。置位的过程只能通过变化单端的CDAC电压来实现阈值的改变。因为对于对于每个电容位的电压只能朝着另一个电压变化,也就是只能增加或者只能减少。那么CDAC的置位过程中,只有一端的电位可以发生改变。

由于在采样过程中正负输入端的下极板都是接VREF,在后续的CDAC置位中无论怎么变化,都是正端或者负端在逐渐下降,那么共模就会在单调下降;

- 第一次采样:上极板=VIP/VIN,下极板=VREF/VREF;

- 第一次比较:直接比较,无需置位,先比较,再置位。如果CMP=1,上极板MSB置0;如果CMP=0,下极板MSB置0;

- 第二次比较:果CMP=1,上极板次MSB置0;如果CMP=0,下极板次MSB置0;

- 第三次比较:...

- ...

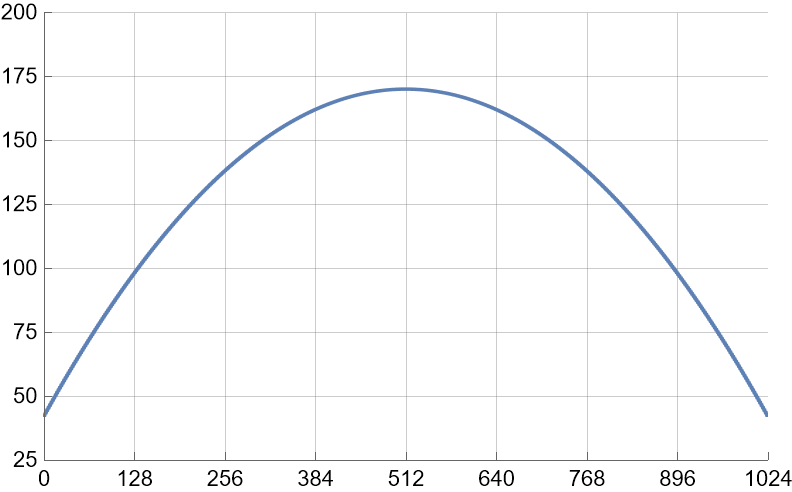

¶ 3.2.2 Mathematic

IMG-Switching-Strategy-and-Power-20241110081005054.nb

Average Energy=255.5

¶ 3.3 Sanyal

¶ 3.3.1 Illustration

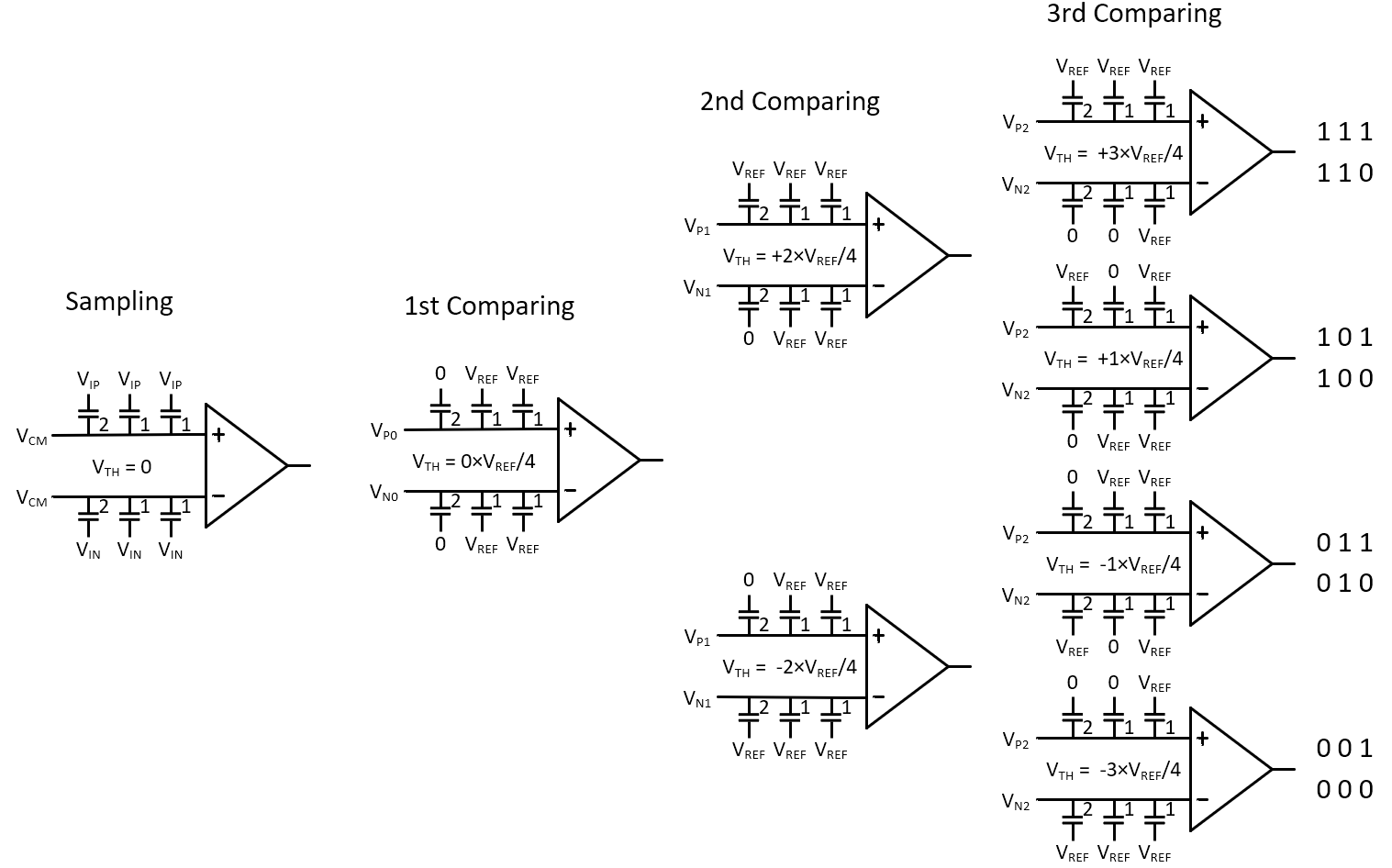

Sanyal这个方案,为了解决输入共模变化的问题,采样时刻让CDAC反馈值的最高bit和剩余bit的初值不一致,那么在后续的CDAC逐次逼近过程中,会出现比较器共模电压先增后减或者先减后增,且后者会逐渐前者。

而且在MSB置位过程中,由于让一端的CDAC全部接入VREF,那么VREF-Driver在变化电容位提供的电荷会通过本来接入VREF的电容位反馈回来。这样几乎一半的CDAC的可以免费置位,相当于可以减少一半的能量消耗

¶ 3.3.2 Mathematic

IMG-Switching-Strategy-and-Power-20241110081005125.nb

Average Energy=127.5

¶ 3.4 VCM-Based

¶ 3.4.1 Illustration

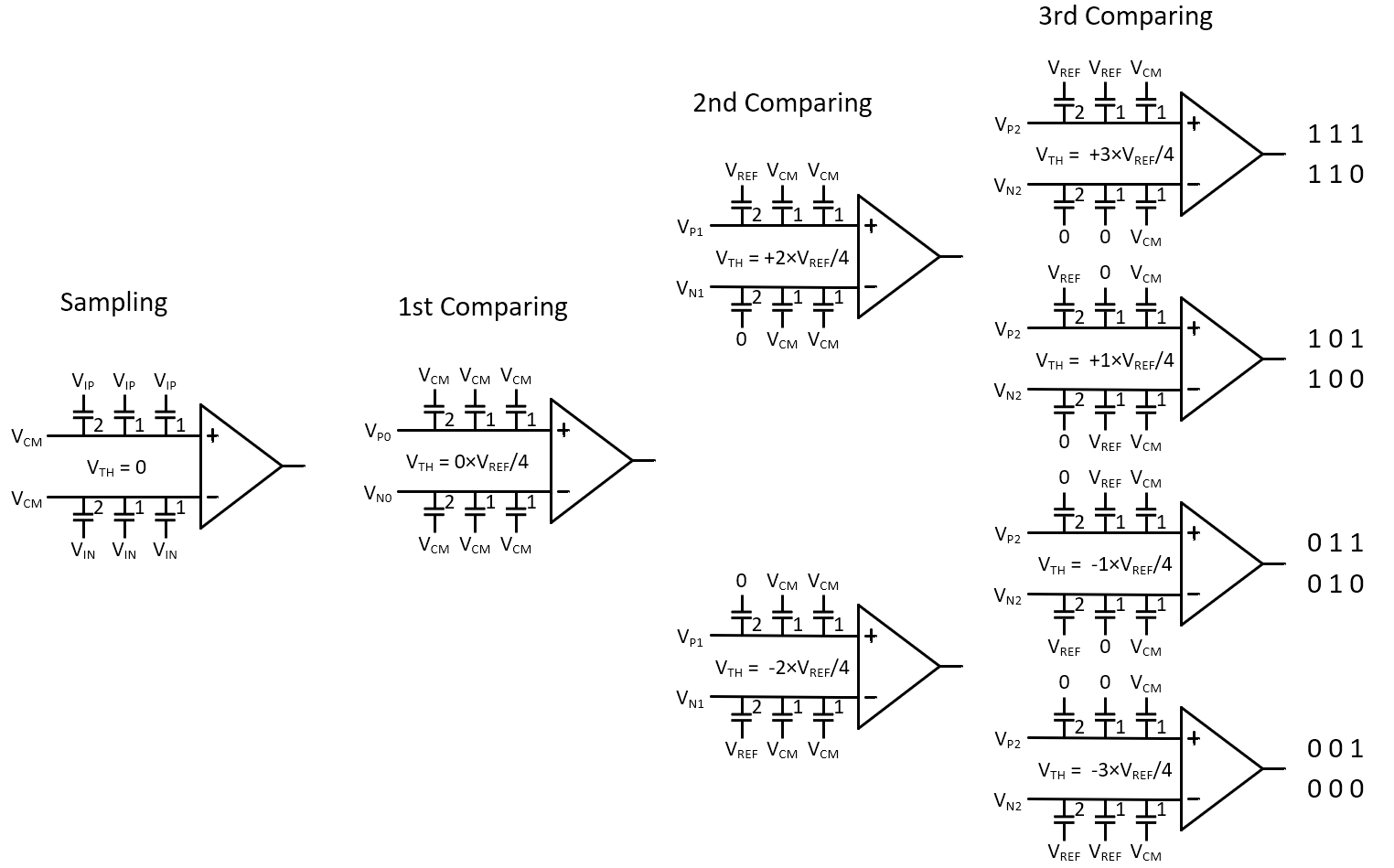

该采样方式彻底解决了每次CDAC切换过程中,比较器输入端共模电压变化的问题。如果保证共模不变,需要做到每次上下极板同时变化,通过一增一减实现差模的置位和共模的恒定。所以通过在采样时刻引入共模,就能实现这一点。这里认为VCM=VREF/2。

¶ 3.4.2 Mathematic

IMG-Switching-Strategy-and-Power-20241110081005209.nb

Average Energy=170.167

¶ 4 Appendix

- VISIO Figure: cdac-structures.vsdx