¶ 参考资料

Vadim Ivanov, Design Methodology and Circuit Techniques for Any-Load Stable LDOs with Instant Load Regulation and Low Noise

¶ LDO 的设计难点

Tutorial 开篇2个问题,都是痛点

- LDOs for digital domains require keeping the output voltage within the error window against instant load switching from zero to maximum current (and back).

- LDOs for analog units may require low noise and large PSRR.

对于先进工艺的 Leakage 问题,Body Bias 似乎是解决思路,但是具有 Push-Pull 也是 LDO 一个非常好的 Feature

- The large drain-source and gate leakage of the core transistors in CMOS processes with a minimum gate length of 90 nm and below create a severe on-chip power management problem.

- Some of these LDOs may control the body biasing inside the power domain. The body biasing demands the bidirectional output current capability.

对于 SOC 系统,无法用太多的外围电容,片上最多容纳 100nF ~ Few nF

- Presence of the 15–20 LDOs in the SoC becomes a common practice. Clearly, use of the external load capacitor for each of these LDOs is prohibitively expensive. We have to learn how to design LDOs while employing the on-chip load capacitors (100 pF to few nF) only.

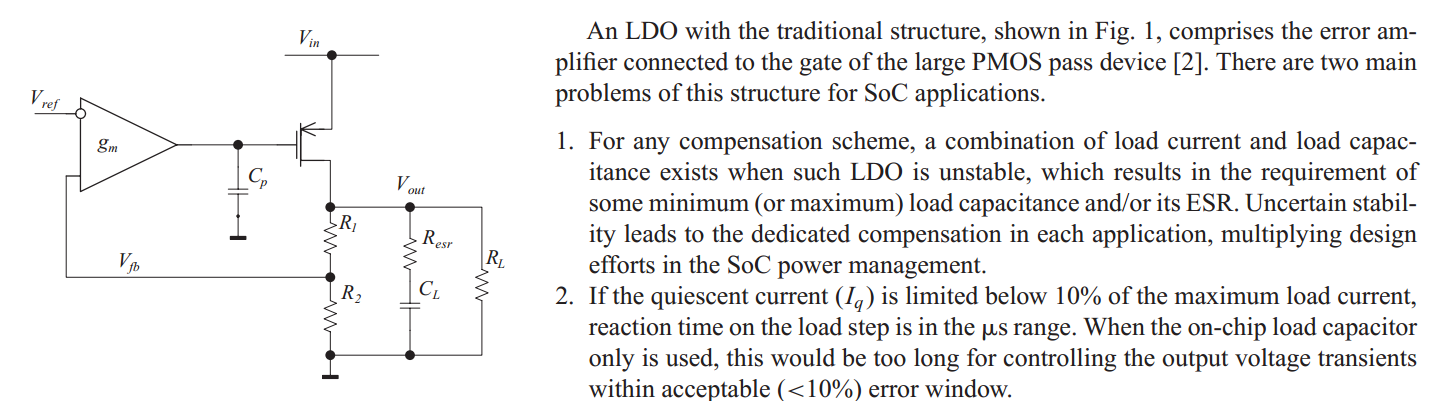

传统的 LDO 具有如下缺点无法解决

¶ Structural Design Methodology

这虽然是一本书,其实来源于一个学术研讨会。Vadim Ivanov 是大师,在讲 LDO 之前,宣讲了他的设计方法学,或者说是设计哲学

This book is part of the Analog Circuit Design series and contains the revised contributions of all speakers of the 17th workshop on Advances in Analog Circuit Design (AACD), which was organized by Andrea Baschirotto and Piero Malcaovati of the University of Pavia. This year it was held at the University of Pavia in the magnificent auditoria “Aula Volta”.

这些设计方法学,对于新人几乎无用。但是对于一个工作近10年的 IC Designer,看完应该会有感触

- 将电路抽象为为信号流的传递,将电路划分为单独的 Unit-Cell,这是非常有益的

- Ivanov 喜欢各种各样的反馈控制,反馈伴随着稳定性问题,他更倾向于使用 transient 的去确认,稳定的系统是可以退化为一阶最多二阶的

- Current Mode 的结构非常优秀,Ivanov 已经不止在一个地方来宣传它了

- 优秀的电路结构,一定是鲁棒的,不需要精心地去调参。如果需要精心调参的结构,那其最优解函数在目标值附近,会非常的 Sharp;我们期望的是 Doll

虽然 Ivanov 承认一些 巧思 能够让满足特定应用,但是经典永远是经典 ,他认为优秀的结构具备以下几个特征

- Good circuit has a dedicated feedback loop controlling each parameter which is important for the reaching of system goals.

- Dynamically each local loop and system as a whole are stable and their step response looks like the response of the system with first- or second-order transfer function.

- Good circuit is robust to the variation of the component parameters, process and temperature.

- Non-linear effects (start-up, power glitch, input/output overload, etc.) have been considered and necessary clamps/limiters added.

- For embedded in SoC designs, good circuit should not be sensitive to substrate noise.

Acceptable application solutions can and sometimes do exist outside of the “good” circuit domain. However, after 30 years of experience, these “no good” circuits could never outperform circuits from the chosen set.

设计一个能正常工作的电路,通常只需要 20% 的时间。其余的时间都在考虑非线性,以及各种意外的保护措施,即 what if。我猜这正是模拟电路需要时间积累的一个原因,或者说是任何一个产品设计都需要面对的课题,设计一个能用甚至性能优异的电路并不难,难的是让他长期大批量使用时,没有问题。

环路稳定性集大成,也是他的 《Operational Amplifier Speed and Accuracy Improvement》这本书的一个具体实践,正是这篇文章

2005_a-110-db-cmrrpsrrgain-cmos-operational-amplifier.pdf

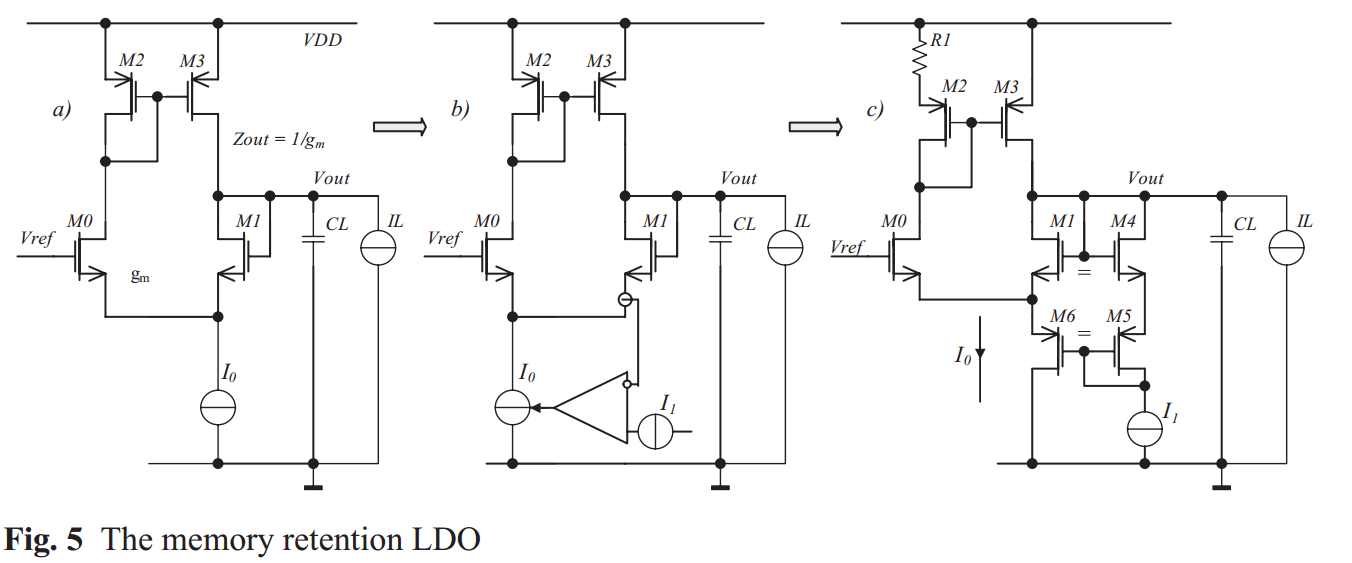

¶ Memory Retention LDO

存储器数据保持 LDO 的设计,是运用结构化方法论最简单的例子之一。在这个应用中,SoC SRAM 模块的供电电压必须保持在一个低于正常工作所需、但足以保存信息的电压值。负载消耗的唯一电流就是 SRAM 模块的漏电流,根据温度和工艺偏差的不同,这个漏电流在几 nA 到几十 μV 之间变化。这里不需要优于 100-150 mV 的精度,也不需要高速响应。如果仅存在 SRAM 内置的旁路电容,LDO 的负载电容可能只有 ;如果使用了片外负载电容,则可能增加到几 μF 。这个 LDO 最重要的参数是静态电流(Quiescent current),必须保持在 200-300nA 以内

(a) 电路的优点是无条件稳定,因为只有一个极点,但是其输出电流受限于 I0;(b) 结构应用动态偏置技术解决了这一痛点;负载电流的上升,会让 M1 的电流减小,通过比较增加了 I0 的电流,再通过 M2-M3 的镜像提高输出电流;至于稳定性,由于这个控制环路是嵌套在主环路的,只要这个小环路稳定,那么主环路就是稳定的

(c) 是一个具体的电路实现。IL 负载电流增大 -> M1电流减小 -> M5 Source 电压减小 -> M5 Gate/Drain 电压减小 -> M6 电流增大 -> 最后通过 M2-M3 镜像出去;M2 的 Source 端的电阻可以让 M2 - M3 形成一个非对称的电流镜,这样可以提高 M2到M3的镜像放大比例

The LDO of Fig. 5c was implemented in TSMC 0.18 process with 100 nA I1 and load current within 10 uA. The maximum error of this LDO, consuming at no-load condition less than 300 nA, is about 100 mV.

¶ The Basic Multiloop LDO Structure

TBD

¶ Low-Noise LDO for Radio Units

TBD

¶ LDO for Digital Units

数字 LDO 的要求如下:

数字单元(例如 SRAM 模块)的电流消耗可以在几分之一纳秒内从零突变到最大值(50 到 100mA),或者反向跳变。为了避免丢失代码,即使在如此陡峭的电流变化下,电源管理电路也必须将该单元的电源电压保持在一个误差窗口内(偏离目标值 50~80mV)。该单元的电源电压由 LDO 提供,并由内置于每个逻辑门中的旁路电容(总计 500–2000pF)提供支持。为了解决这个问题,LDO 对负载变化的反应时间不应超过 4–6ns。由于键合线(wirebond)和电路板总线电感的存在,片外电容对于这项任务几乎毫无价值,因为在负载和电容之间总共 5–10nH(总线+键合线+电路板)的电感上,会产生 100mV 或更大的瞬态电压尖峰。

在具有大电流消耗(约为最大负载电流的 10%)的双环路 LDO 中,已经实现了足够快的负载瞬态响应。

P. Hazucha, T. Karnik, B.A. Bloechel, and C. Parsons “Area-efficient linear regulator with ultra fast load regulation,” IEEE JSSC, v. 40, # 4, pp. 933–940, April 2005.

由于数字单元可能会长时间处于启用状态,因此这种级别的消耗对于电池供电的设备来说是不可接受的,其静态电流应该低于 50–100uA;并且对双向电流的跳跃反应时间都在 4~5ns 这个时间内

¶ Verification of the Stability with CAD Tools

核心思想是使用 Transient Simulation,利用二阶 STEP Response 公式的阻尼系数和系统频率去评估稳定性;Invanov 认为,AC 仿真是在以前计算资源不足的情况下的一个简化/折衷的方法,但是实际电路涉及到大量的非线性,Transient Simulation 才是最靠谱的。

TBD