¶ 专利基本信息与背景

该专利是针对上一代 Butterfly Shuffler 技术的重要演进,专门解决三电平(Tri-level)DAC 的失配整形问题

- 专利文件:US7079063_TRI-LEVEL-SHUFFLER.pdf

- 专利名称:System and Method for Tri-Level Logic Data Shuffling for Oversampling Data Conversion

- 发明人:Khiem Quang Nguyen (Tewksbury, MA), Richard Schreier (North Andover, MA)

- 受让人 (机构):Analog Devices, Inc. (ADI)

¶ 整体结构

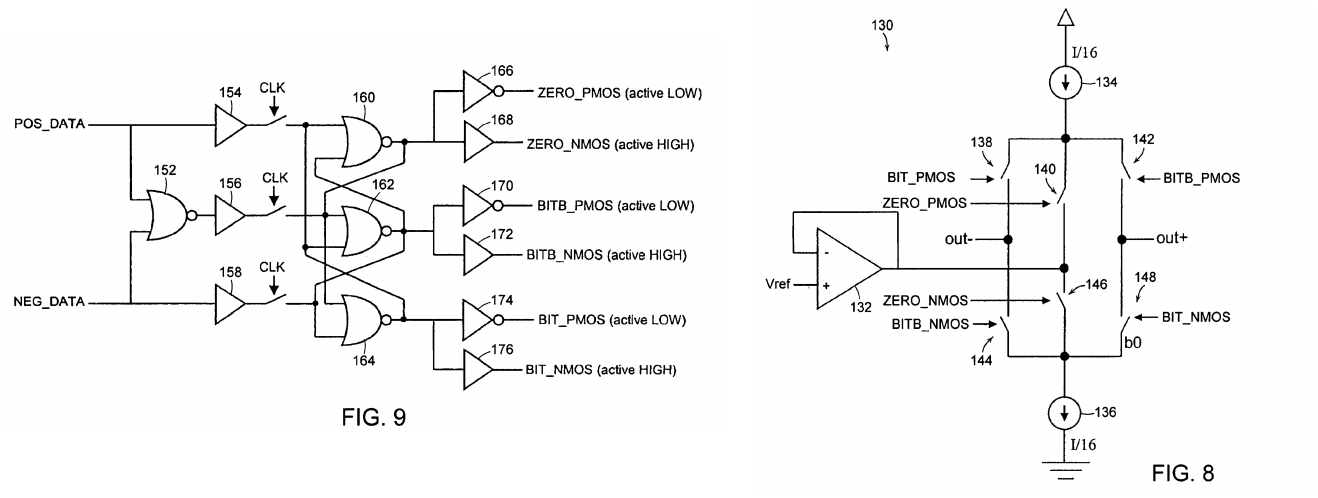

这里要处理的 Element 是有3个 Level 的,具有 +1, 0 -1,如下图这个 Tri-Level 的 Current DAC Element,对于这个 Element,具有3个状态,而不是2个状态,因此需要考虑 Tri-Level 反馈

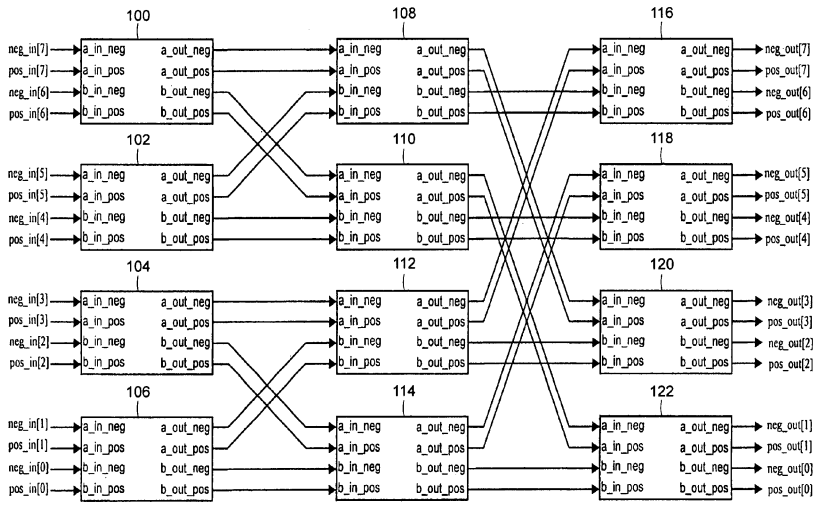

在进入下面这个 DEM Butterfly Shuffler 前,需要把信号转换成温度计码 pos_in[7:0] 和 neg_in[7:0], pos_in[7:0] 的个数表示有多少个 +1,neg_in[7:0] 的个数表示有多少个 -1,这样可以表示的范围就是 -8 ~ 0 ~ +8 共 17 个 Level

¶ 如何处理 +1, 0, -1

要理解这项技术,首先需要明白它与 Bob Adams 的早期 Butterfly(US 5,404,142)的区别。早期的 Butterfly 处理的是二值逻辑(0 和 1),即“开”和“关”。而这项专利处理的是有符号数据(Signed Data),即每个单元有三种状态:输出正电流(+1)、输出负电流(-1)或关断(0)。

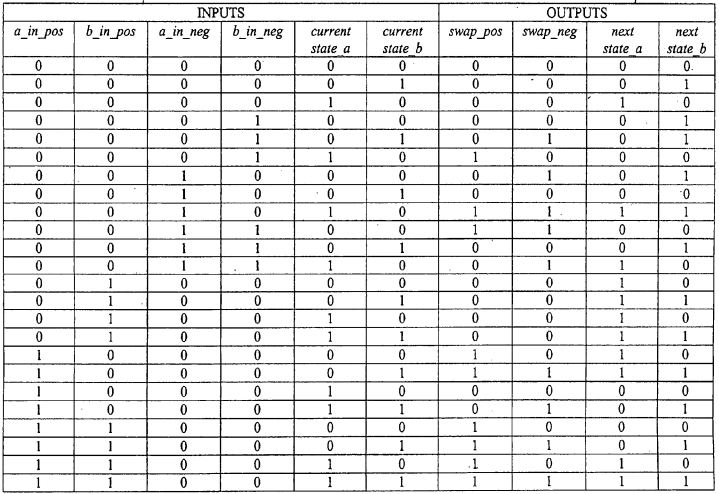

在传统的二值 Butterfly 中,我们只需要保证“1”被均匀地分配到不同的单元上。但在三电平系统中,我们面临两个独立的任务:必须保证所有的“+1”被均匀分配到正电流源上,同时必须保证所有的“-1”被均匀分配到负电流源上。与之前的专利相比,这里的“积分器”逻辑发生了变化。之前的专利:使用一个积分差值(Count A - Count B),状态通常被限制在 0 和 1(或 -1, 0, +1),用于平衡“开”的次数。本专利:采用了双状态位机制。如图 4 所示,核心单元包含两个触发器,分别产生 state_a 和 state_b

state_a:专门记录正输出的使用历史。如果state_a为 1,表示上一次的正电流(+1)是由上路输出端(Out A)承担的。state_b:专门记录负输出的使用历史。如果state_b为 1,表示上一次的负电流(-1)是由下路输出端(Out B)承担的 。

这意味着系统不再是维护一个单一的“差值”,而是维护两个独立的“指针”,分别指向下一个该轮到谁去输出正电流,以及下一个该轮到谁去输出负电流

¶ 交换逻辑的通俗理解

下图真值表看起来很复杂,但其背后的逻辑可以用一种非常通俗的“轮班制”来解释。我们可以把交换单元看作一个分流器,它要把输入的任务分配给后面两个工人(A 和 B)。

假设系统来了任务:

-

输入有一个 +1(正电流任务) 系统会查看 state_a(正任务记录本)。

- 如果记录本显示“上次是 A 干的”(state_a = 1),那么这次逻辑电路就会控制开关进行交换(Swap),强制把这个 +1 任务分配给 B。

- 如果记录本显示“上次是 B 干的”(state_a = 0),那么这次就不交换,把任务给 A。

- 果:A 和 B 轮流承担输出正电流的工作,实现了正电流源的匹配。

-

输入有一个 -1(负电流任务) 系统会查看 state_b(负任务记录本),逻辑与上面完全一致。A 和 B 轮流承担输出负电流的工作。

-

输入是 0 没有任务,保持状态不变或者复位,大家休息。

-

特殊情况:输入有两个 +1 既然 A 和 B 都要干活,那就直接直通,不需要交换,状态也被标记为“平衡”(因为两个都被用了)。

总结:这个真值表的本质就是两个独立的“乒乓”开关。一个乒乓开关负责把输入的 +1 均匀打到两路,另一个乒乓开关负责把输入的 -1 均匀打到两路。这就是为什么图 4 的电路比之前的 Butterfly 复杂,因为它实际上是在同时跑两套 Shuffling 逻辑。

¶ 一阶整形与平均分配的实现

本质上,这依然是一阶整形。在信号处理中,失配误差(Mismatch Error)来自于电流源的实际值与理想值的偏差。

- 对于 +1,误差是 epos

- 对于 -1,误差是 eneg

该专利的 Shuffler 实际上是在对 epos 和 eneg 分别进行一阶噪声整形。通过上述的“轮班”机制,长期来看,任何一个单元输出 +1 的概率与其他单元是相等的,输出 -1 的概率也是相等的。 这就保证了:

- 正电流源之间的失配误差被推到了高频。

- 负电流源之间的失配误差也被推到了高频。

所以,虽然有正负之分,但数学原理没有变:通过基于历史状态的轮选,确保每个元件的使用频率(Usage)与输入信号的平均值一致,从而使误差积分(累积使用次数之差)有界。只要积分有界,就对应于一阶噪声整形。

¶ DEM 的缺点分析

尽管这个三电平 Shuffler 看起来很完美地解决了正负电流源的独立匹配问题,但它依然存在一些显著的缺点,这也是后来更高级算法(如分段 DWA 或树形结构优化)出现的原因:

-

硬件复杂度与面积激增 对比 Bob Adams 的专利,本专利的每个交换单元(Cell)极其复杂。图 4 显示,一个单元需要两个 D 触发器、两个 NOR 门、四个 XOR 门、两个 AND 门和一个 NAND 门 。而在传统的 Butterfly 中,一个单元可能只需要一个触发器和几个门。 对于一个高位数的 DAC(例如 5-bit 或 6-bit),这种单元的数量是庞大的(N * logN 级别)。这会导致芯片面积显著增加,布线拥堵。

-

关键路径延迟(Latency) 这依然是一个多级级联结构(图 6 和图 7 展示了多级互连)。信号必须从第一级穿透到最后一级才能到达 DAC 驱动器。由于每个单元现在的逻辑门延迟比以前更多(逻辑深度增加了),这会限制 DAC 的最高工作频率。在高速应用中,这种复杂的组合逻辑链可能成为时序瓶颈。

-

潜在的模式噪声(Tone)与对随机化的依赖 虽然设计了“轮班”机制,但在某些特定的输入模式下(例如输入总是 +1, 0, +1, 0...),状态机可能会陷入固定的循环,导致频谱上出现杂散音(Tone)。 专利发明人也意识到了这个问题,所以在图 1 的系统框图中,特别在前端增加了两个 "Random Barrel Shifter"(随机桶形移位器) 。这说明单靠后端的 Butterfly Shuffler 自身,可能无法完全打散输入信号的相关性,必须依赖前端的随机预处理来辅助“去相关”。这进一步增加了系统的复杂度和功耗。

-

针对 0 输入的优化带来的代价 这个专利的初衷是为了支持 Tri-level DAC(即 0 输入时关断电流以降低噪声)。虽然它成功实现了这一点,但也引入了复杂的“有符号温度计编码”逻辑。这种架构在低信号电平下(很多 0)信噪比很好,但在大信号下,复杂的开关动作可能会引入额外的时钟馈通(Clock Feedthrough)或电荷注入误差,这些动态误差有时比静态失配更难处理。