¶ 综述与架构原理

¶ 摘要与性能指标

来源于2015年 KAIST 的一片 JSSC 论文,从功耗效率和面积效率上,似乎有些偏低,但是这是几乎没有异构的SAR,没有用 Time-Interleaved 的技术

- 参考文献:2015_JSSC_A_Decision-Error-Tolerant_45nm_CMOS_7b_1GSs_Nonbinary_2bCycle_SAR_ADC.pdf

- 性能指标:CMOS 45nm,1.25V VDD,1GS/s,7bit Resolution,40.8dB SNDR,0.016mm2

摘要:本文提出了一种紧凑的、容忍判决错误的 2位/周期(2b/cycle)SAR ADC 架构。实现了两个具有不同指定功能的 DAC,即 SIG-DAC 和 REF-DAC,以使结构紧凑并消除采样偏差问题。使用带有判决冗余的非二进制判决方案,不仅通过放宽 DAC 建立要求提高了 ADC 速度,还使性能对参考电压波动和比较器失调变化具有鲁棒性。提出的动态寄存器和直接 DAC 控制方案通过最小化 SAR 判决环路中的逻辑延迟提高了转换速度。此外,提出的带有数字误差校正的比较器误差检测方案增强了高速 ADC 的性能。基于 45 nm CMOS 工艺制造的原型 7位 ADC 在 1.25 V 电源下以 1 GS/s 的采样率运行,峰值 SNDR 达到 41.6 dB,并在高达 1.3 GHz 的信号频率下保持有效位数(ENOB)大于 6。在 1.25 V 电源下,其优值(FoM)为 80 fJ/转换步,功耗为 7.2 mW

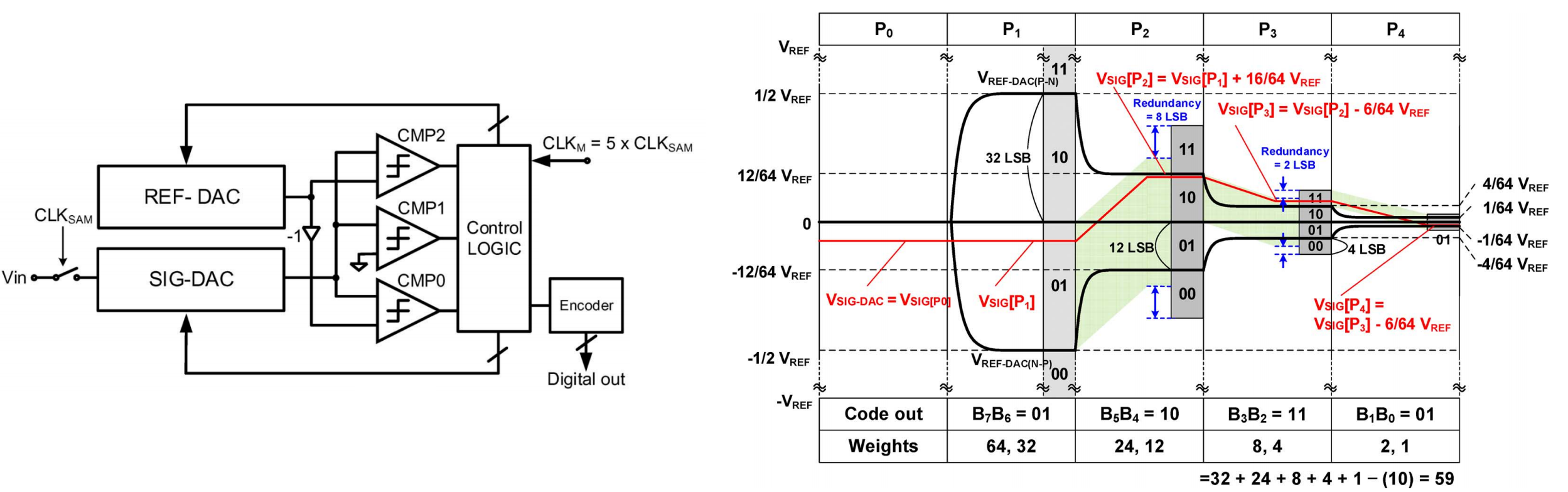

¶ 架构原理

基本原理如下:

- 首先每次比较用 3 个 Comparator 实现 2bit/Cycle 的效率。

- 整体分成了 2 个 DAC, SIG-DAC 采集数据,并做每次的 subtract, REF-DAC 每次比例衰减,这样缓解了 SIG-DAC 大信号建立压力。简单来说,传统的 SAR,每次比较完,比如发现大于 1/2 REF了,那 SIG DAC 就需要减去 1/2 REF,在这里下一次我将 REF 衰减为 1/4,那我要减去的就不是 1/2 REF了,而是 1/2 × 1/4 了。

- Non-Binary 的权重,冗余了 1bit:P1第一次比较,B7B6 代表 64/32,但是在接下来的 B5B4 的权重是 24/12,而不是 16/8,冗余是基本操纵了。但是这里的冗余,24=16+8,12=8+4,这个不仅权衡了误差点与比较阶段的关系,还使用了 二进制的组合,这样在接下来的处理种,可以使用 binary 的二进制加法器,快速地完成冗余位的处理。整体上,总的权重不是 128,而是148,最后的结果还原到二进制时,要减去10

至于为什么时减去10,而不是20,之所以只减去 10,是因为在总共 20 LSB 的冗余中,只有 10 LSB 的冗余是加在量程“下侧(lower side)”的。 这 20 个单位的冗余并不是全部分配在同一侧,而是被上下平分了;当 ADC 将非二进制权重(64, 32, 24, 12, 8, 4, 2, 1)累加输出一个数字码(例如论文图例中的 69)时,这个数值是从量程的最底端(0点)开始向上计算的;上侧的 10 LSB 就像是给身高尺顶部加长的一段,只要你的身高没超过上限,这段加长对你的读数没有任何影响;但下侧的 10 LSB 就像是把踩着的垫子抽走了一截,导致读数凭空变大了 10。因此,最后修正时只需要把垫子的高度(下侧的 10 LSB)减掉即可,不需要减去 20

按照步骤理解这个过程:

- P0 采样阶段;

- P1 第一次比较,比较发现信号处于 01 这个区间,信号处于 -32/64 ~ 0 这个区间段,我们认为此时其实信号处在 -16/64 这个区间,因此把信号加上 +16/64

- P2 阶段,首先将 VREF 衰减4倍,因为我们已经进行了 2bit 的量化,原则是可以这么做的。但是为了冗余,将 VREF / 4 后又扩展了 8 LSB。

- P2阶段比较出的值等于10,意味着信号处于 0 ~ +12/64 这个量级,中心值是 +6/64,所以下一次减去 +6/64

- ...

¶ 电路实现

¶ SIG-DAC & REF-DAC

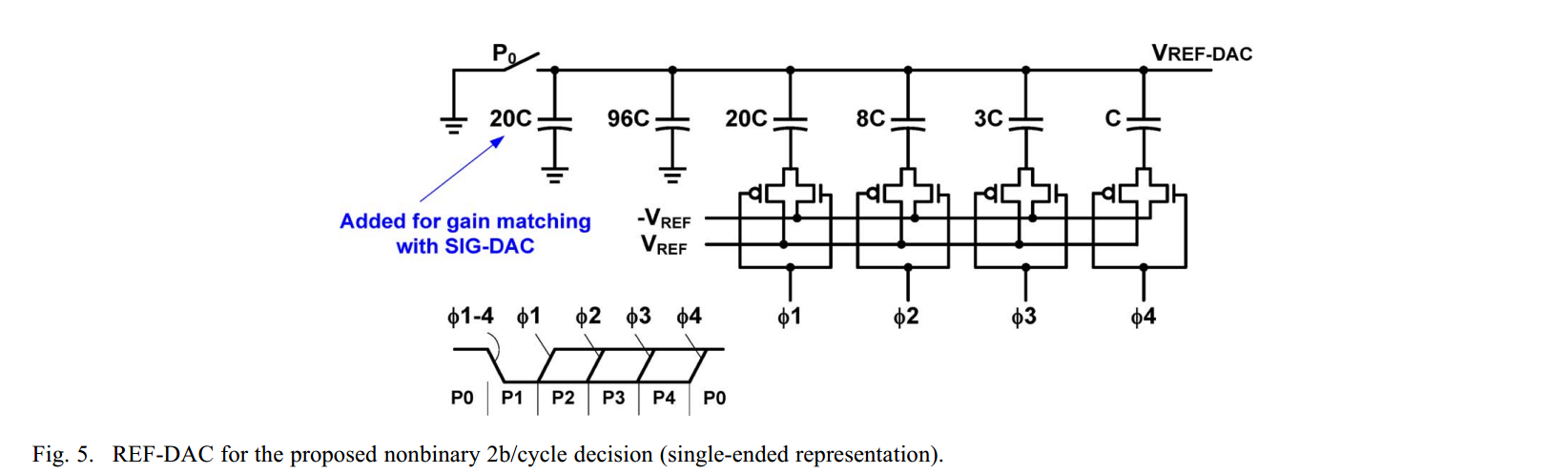

REF-DAC 比较简单,因为每次都是固定已知的比例在衰减。由于 SIG-DAC 多出了 20C,每次在进行上述的比例运算时,真实信号的分母不是 128,而是148,所以为了实现 Gain-Matching, REF-DAC 上也加了20C

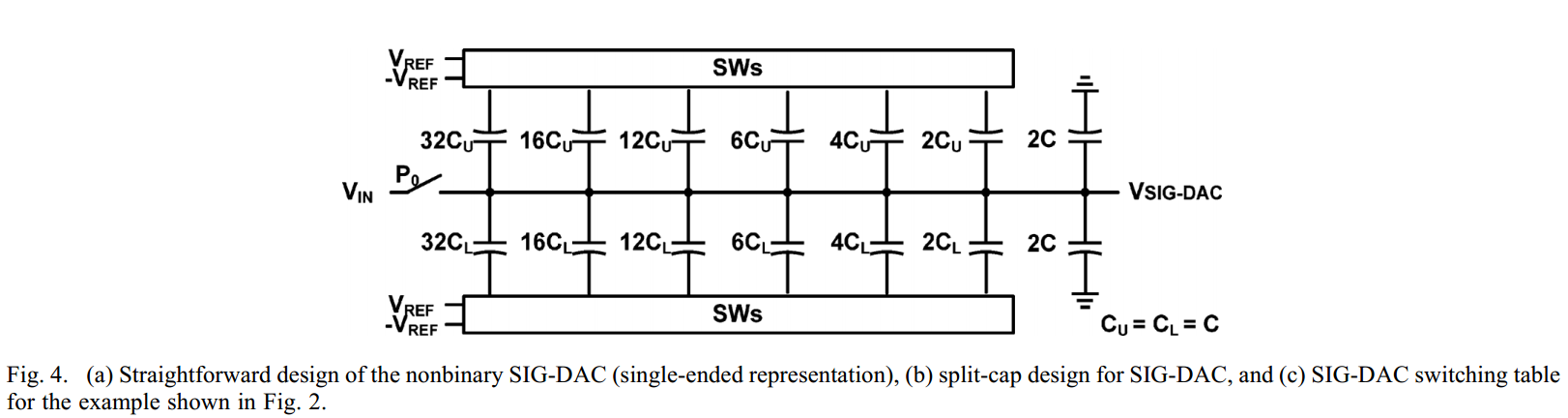

SIG-DAC 按照权重,使用了 Spit-Cap 的设计方法。P0采样阶段的时候,上面全接 +VREF,下面全接 0,之后的变化,如果要减去,就是上面的 +VREF -> 0;如果加加上,就是下面的 0 -> +VREF,实现了单调的变化。

在传统的标准二进制 SAR ADC 中,DAC 进行模数转换的过程本质上是一个“试探与纠错”的过程。在测试某一个比特位(例如 MSB 最高位)时,DAC 会先盲猜这一位是“1”,因此把对应的巨大电容从地(GND)切换并连接到参考电压(VREF),较器比较后,如果发现加上的这个权重太大了(即输入信号实际上比较小),系统就必须承认错误,撤销刚才的操作。于是,必须把这颗刚才连到 VREF 的电容重新切回到 GND。这个“切上去又切下来”的撤销动作,就是 Switch-back。每次把电容连到 VREF 时,电源都在给电容充电;一旦发现猜错了又要切回 GND,这些充进去的电荷就会直接被泄放掉白白浪费。频繁的充放电会导致极大的动态开关功耗

论文中使用的 Split-Cap 架构彻底摒弃了“试探与撤销”的逻辑,改为“单向操作”。在 Split-Cap 结构中,代表某个权重的单个大电容被物理劈成了两半。在采样阶段结束准备转换时,所有的 CU 默认全部接在 VREF上,所有的 CL默认全部接在 GND 上。这相当于系统初始时就稳稳站在了量程的绝对中心(即实现了传统电路中 VCM的效果,但完全不需要真实的 VCM 电源)

因为 Split-Cap 提前把电容劈成两半并分别接在了高低电平上,它把原本需要在三个电平(VREF, VCM, GND)之间来回横跳的操作,变成了只在 VREF 和 GND 之间进行的“单向坠落或单向攀升”。这种单向动作彻底消除了撤销重来的 Switch-back 操作,从而极大降低了功耗,并且因为自带中心点效果,也彻底省去了额外生成 VCM 电压源的麻烦

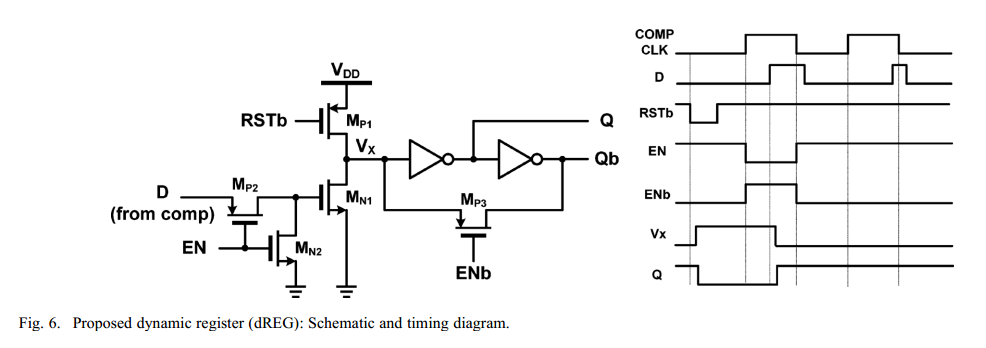

¶ Dynamic Register & SIG-DAC

Register 这个 D 触发器,复位 Vx=1,Q=0;传递的时候只能传1,0是不会通过的,因为Mp2 只能通过高电平,后面的两个反相器,以及正反馈 Mp3,能够强力维持的是 1,0 其实只是微弱维持,这样 D 端的输入想改变输出时,时可以做得到的。

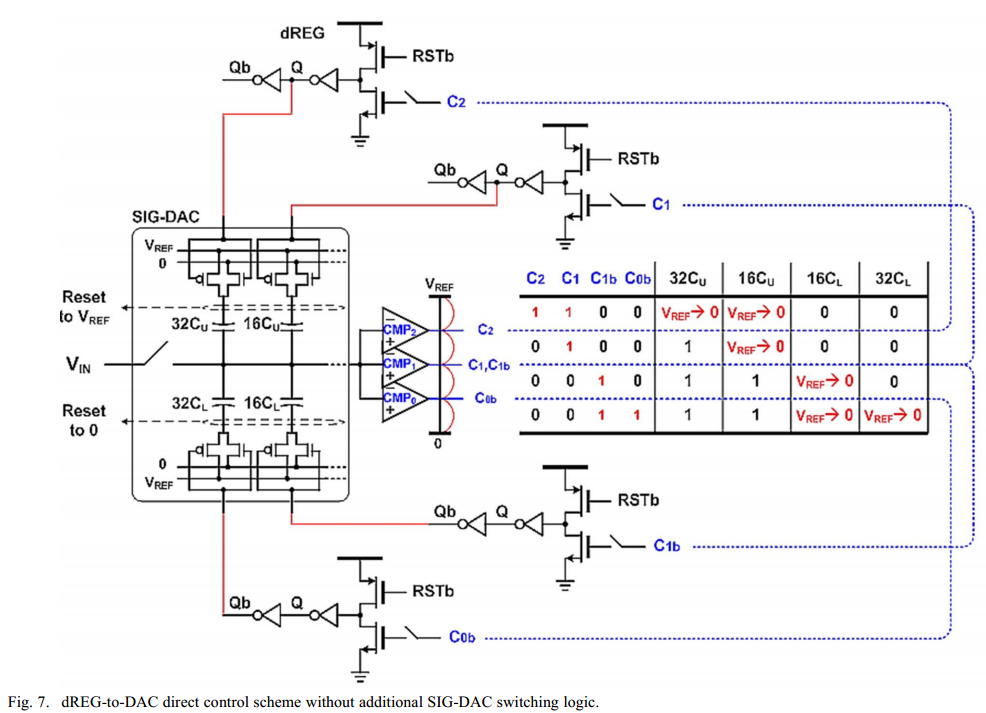

这个触发器可以直接与 SIG-DAC连接,以下这个过程是 P1 相位比较完后,P2 相位 SIG-DAC 加减的动作。可以从表格中看到:

- 如果比较器 B7/B6=11,意味着上面是 32CU 和 16CU 都要从 VREF -> 0 ,完成 -48/64 的操作

- 如果比较器 B7/B6=10,意味着上面的 16CU 要从 VREF ->0,完成 -16/64 的操作

- 如果比较器 B7/B6=01,意味着下面的 16CL 要从VREF ->0,完成 +16/64 的操作

- 如果比较器 B7/B6=00,意味着上面是 32CL 和 16CL 都要从 VREF -> 0 ,完成 +48/64 的操作

完整的差分结构以及控制时序如下

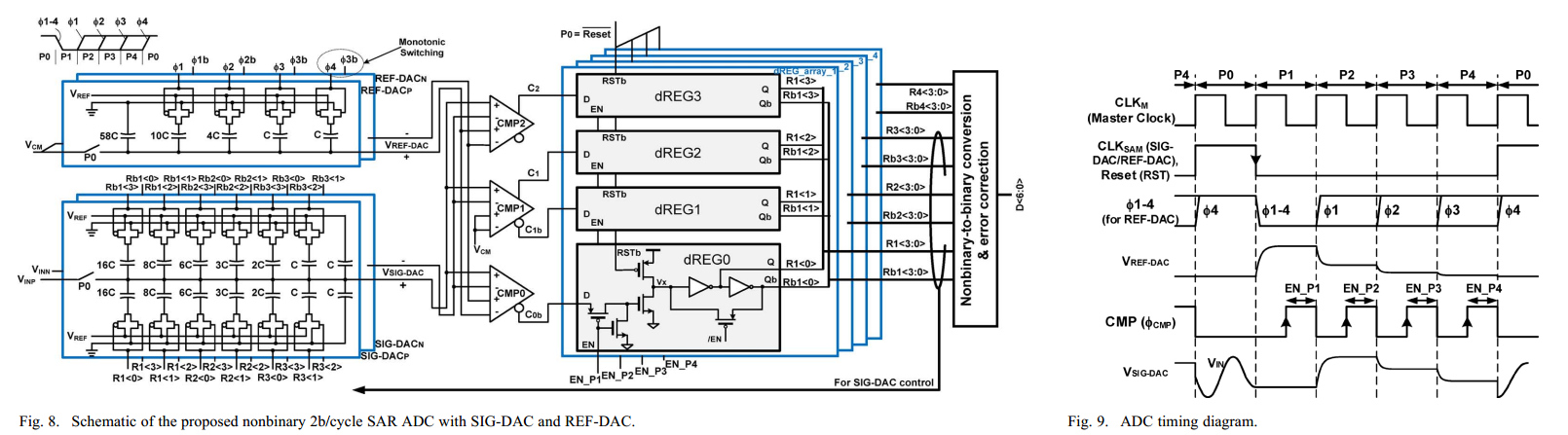

- 比较的4个相位,需要记录4次结果,分别是 P1 P2 P3 P4,因此需要 4 组 dREG,每一组包含 4 个 dREG0~dREG3 去控制 SIG-DAC

- REF-DAC 还是需要 VCM 的,但是这个 VCM 是内部的;如果与输入共模不一致的话,那这个比较器工作状态是值得怀疑的。当然这个比较器是有一个前台校准的,但是作者没有考虑这个问题,或许在 SOC 系统中,默认了 输入信号共模是 VCM 是一致的

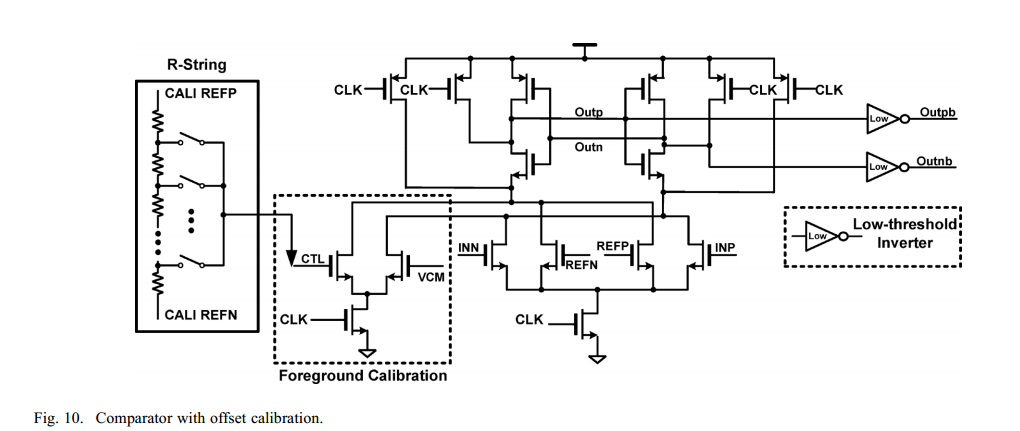

¶ Comparator & NCE

比较器的结构如下,额外增加了一个失调调整的 R-String,以及输出级使用 Low-threshold Inverter。这个 Low-threshold Inverter 表示这个比较器,除非输入电压很低,否则输出总是保持为 0,这个0 接到 dREG 的输入的那个Mn2上,其实就是代表着不动作;

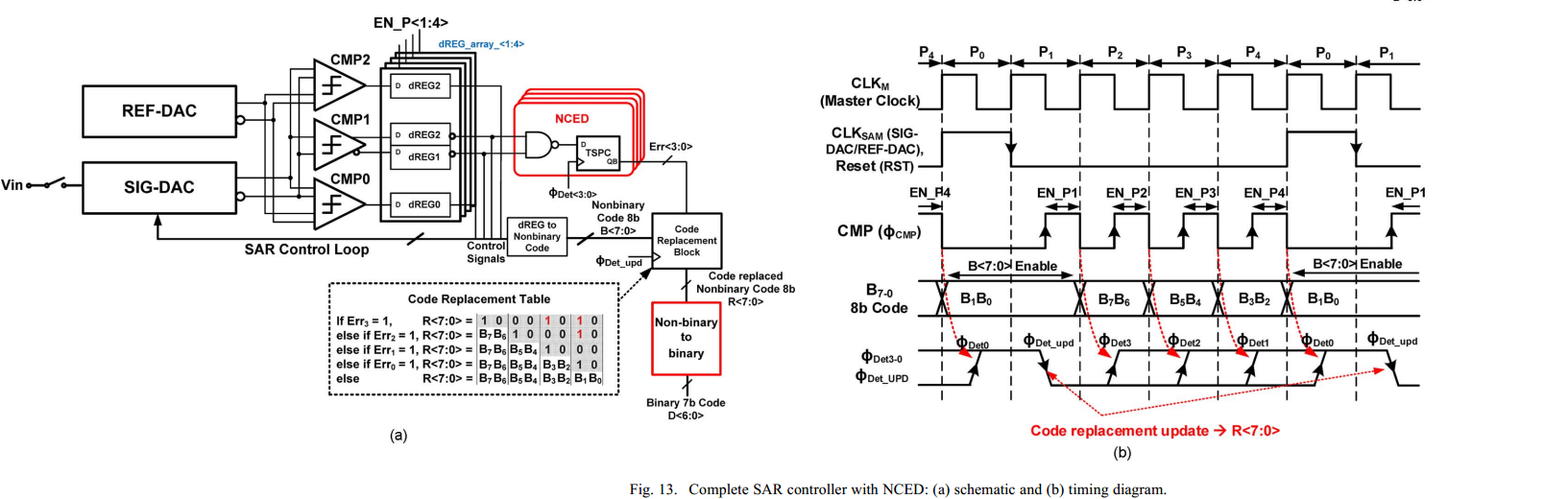

从 Fig.7 中我们知道,对于中间这个比较器 CMP1,是需要用到 Complementary Output 的,也就是这个差分电压一定是有1有0,如果不能保证这一点,就发上了 Non-Complementary Error,接下来的切换机制就错了。为了保证有这个纠错能力,做了上面的 Low-Threshold Inveter,如果出错了,那两个输出都是 0,这样 SIG-DAC 不动作。但是 后面有一个 Non-Complementary Error Detector (NCED) 发现这一点,从那个阶段错了,就把后面的转换结果全面丢掉,替换成一个预设的 Residue 几乎为 0 的一个 Code,也就是下图中左边这个 Code Replacement Table 所表示的那样

这篇文文官员 NCE 的纠错,是不在环路内的,而是在环路之外,比较完成了之后最后去替换,不是实时调整,这样的好处是避免了 NCED 这个逻辑影响反馈速度。

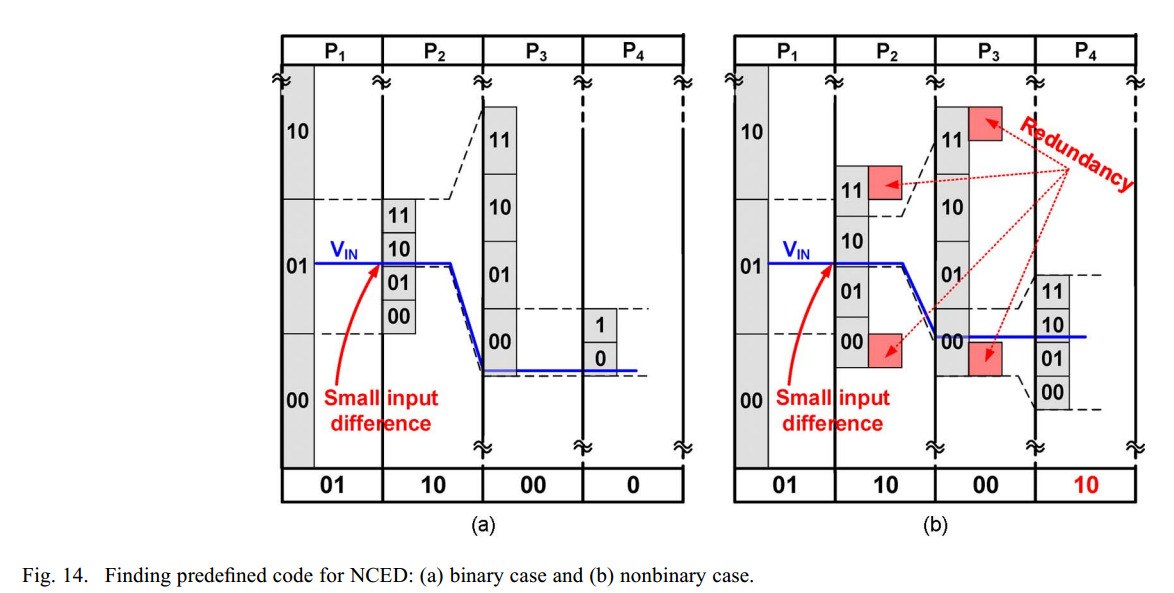

这个替换,Binary Code 与 Non-Binary Code 不一样,大概思路还是一样的,其实就是认为在这个阶段,CMP1 的 INPUT 约 REF 非常接近了,无法在规定时间建立,所以此时的 Residue 几乎为0了,至于这个 Residue 怎么为0,Non-Binary 编码下是不一样的

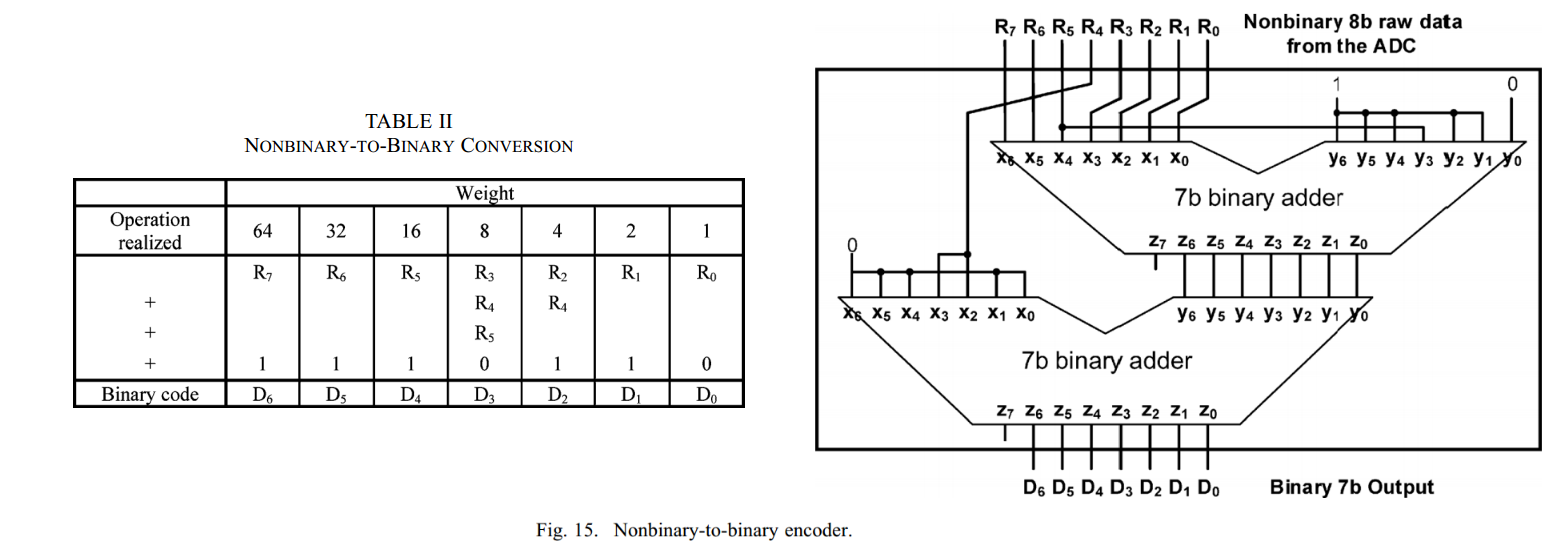

¶ Redundant Non-Binary Binary

最后需要将冗余的码值,转换成二进制码的。由于我们的冗余位置,B5 其实 = 16+8 = 24,B4 = 8 + 4,所以可以轻松地通过 7b binary adder 完成求和。最后减去 10 这个动作,在模128(7bit)系统中,+10 的二进制码 0001010 补码,即取反+1后等于 1110110,可以看到 Fig15 两个 7b 半加器实现了这一点,抛弃 z7 的操作实现了模 128 运算。