- Reference: A 0.4uW/MHz Reference-Replication-Based RC Oscillator with Path-Delay and Comparator-Offset Cancellation Achieving 9.83ppm/°C from -40 to 125 °C

- ISSCC 2025

- Frequency: 10MHz

- Process: 65nm CMOS 1V

- Power: 0.8V

- Temperature Coefficient: 0.12408% for -40°C ~ 125°C

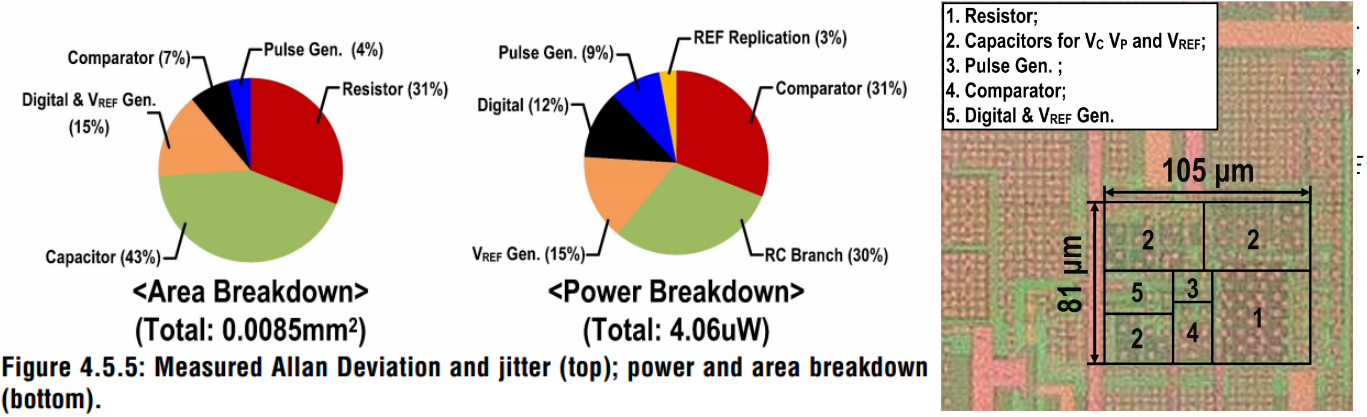

- Area: 0.0085mm2

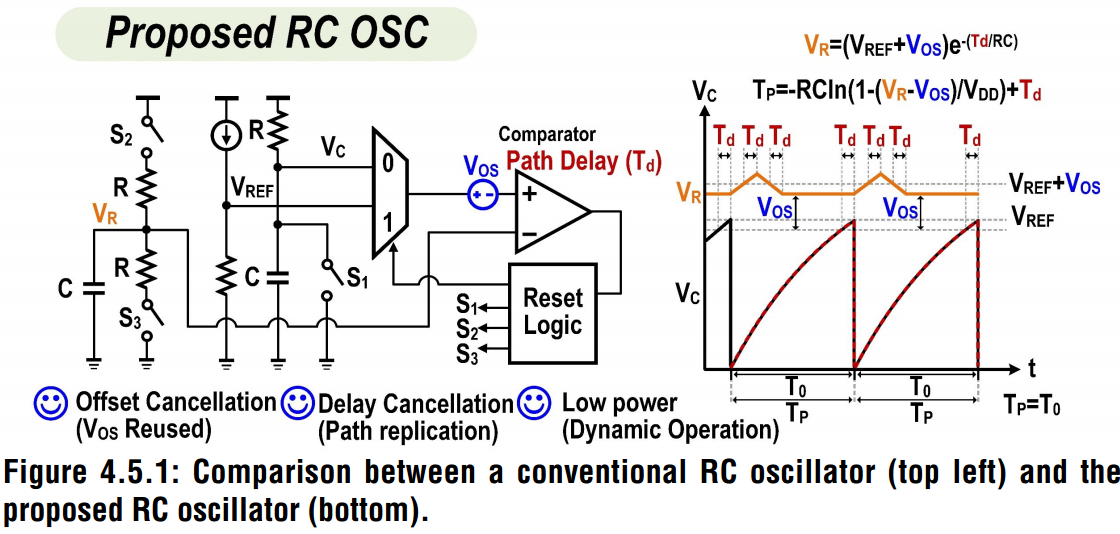

¶ Proposed Structure

| 比较器输入MUX | VR行为 | VC行为 | VREF行为 | 比较器输出 | |

|---|---|---|---|---|---|

| 0 | VIN+=VREF;VIN-=VR | 向上充电 | 从0开始向上充电 | R/2R分压 | 1 -> 0 |

| 1 | VIN+=VREF;VIN-=VR | 向下放电 | 继续向上充电 | R/2R分压 | 0 -> 1 |

| 2 | VIN+=VC;VIN-=VR | 高阻保持 | 继续向上充电 | 高阻保持 | 1-> 0 |

| 3 | VIN+=VC;VIN-=VR | 高阻保持 | 继续向上充电 | 高阻保持 | 0-> 1 |

| 4 | VIN+=VREF;VIN-=VR | 向上充电 | 短暂pulse复位至0 | R/2R分压 | 维持1 |

- STEP 0 和 1:用于将 VREF 复制到 VR 上,但是这里的 VR 包含了 VOS 和 的信息。 优秀的点在于复制了比较器正向翻转过程的 Vos 和 Td,略微的瑕疵(或可忽略)的点在于 RC Ramp 信号在 VREF=VDD/2 上下充放电斜率是不一致的(RC-RAMP信号有先快后慢的特点),预计 Vos 复制是准的,Td 的复制略有瑕疵

- STEP 2 和 3:RAMP 信号 VC 和 VR 的正常比较过程

- STEP 4:VC 的复位时间。 这个非常不好,因为这个这个复位时间是逻辑门的 Delay,正温度系数且贡献在周期内

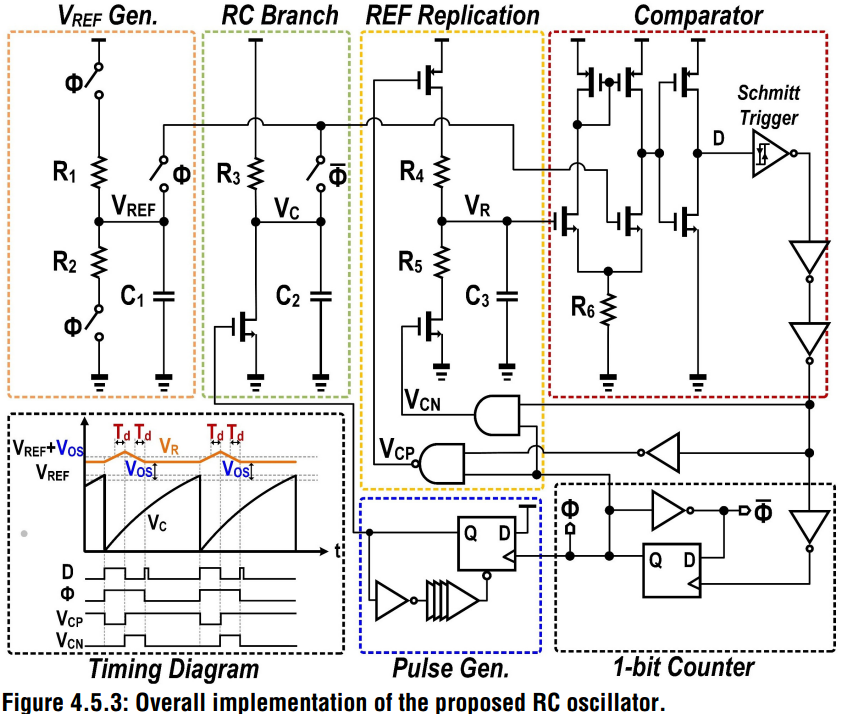

¶ Circuit Implementation

我们观察到:

- 现在流行 Resistor Capacitor 作为 Ramp,而非 Current - Capacitor:优势在于节省了 IBIAS 电路以及避免了 Current Source 的高噪声;

- 固定VDD,意味着 R6 的压降是确定的,所以比较器的电流为 (VDD/2 - Vthn)/R

- 40um × 50um 的电容,意味着 2pF ~ 4pF 的电容,电容还是比较大的;可以抑制开关的寄生电容以及 Charge Injection

- 比较器的功耗优化,虽然 Td 不是问题, 但是 Ramp 信号整形为快速数字信号,比较器的功耗优化设计有待考虑

¶ 论文复现

初步以 0.18um 1.8V 器件搭建电路仿真,仅实现 1% 的 Typical TC,周期与温度成正比,偏向于认为是 Logic Gate Delay 的影响;另外搭建的电路,电容取 1pF 也比较小,如果不进行 TC Trim 的条件下,预估优化后勉强达到 0.5% 的 TC