Reference: A 32-MHz, 34-μW Temperature-Compensated RC Oscillator Using Pulse Density Modulated Resistors

Download: 2022_JSSC_A_32-MHz_34-_u_W_Temperature-Compensated_RC_Oscillator_Using_Pulse_Density_Modulated_Resistors.pdf

这篇论文提出了一种基于频率锁定环(FLL)架构的高能效片上时钟源,通过引入脉冲密度调制(PDM)控制的开关电阻网络,解决了传统电阻阵列在温度补偿中面临的非线性和开关漏电问题。

- 65nm Process

- 32MHz,34uW/1.1V = 31uA

- -40°C ~ 85°C,0.16%

- Area = 0.18 mm^2

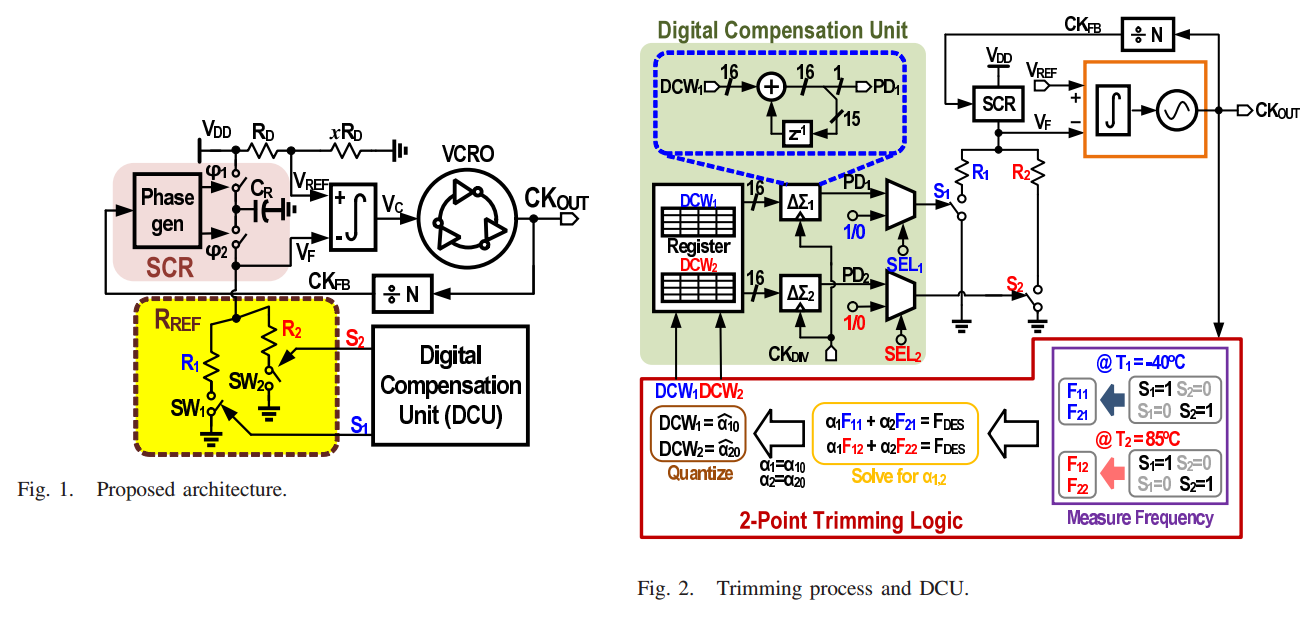

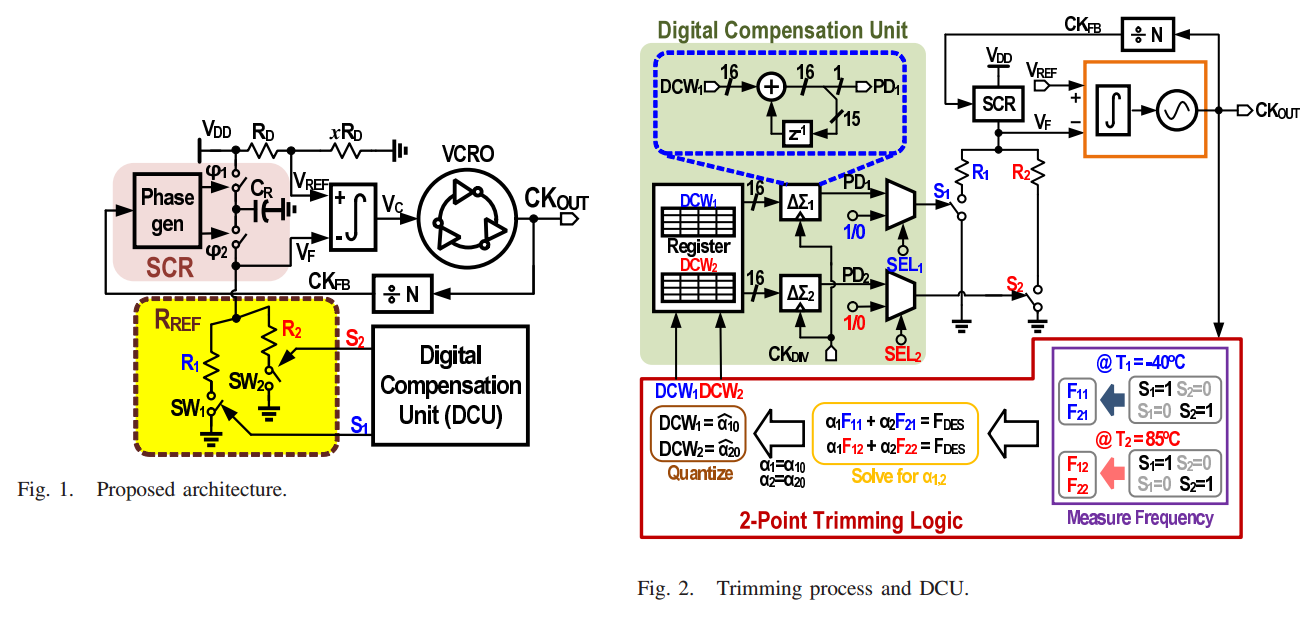

频率锁定环(FLL)振荡器是一种利用负反馈回路将压控振荡器(VCO)的频率锁定在由片上电阻和电容定义的时间常数上的全集成时钟源。利用开关电容技术将频率转换为电流并与参考电流进行比较,从而实现对温度和电源电压不敏感的频率锁定的基本架构。

观察左图,上面 RD 和 xRD 构成了分压电阻,得到 VREF

VREF=VDD×xRD+RDxRD=1+x11

Switch + Capacitor 构成了一个等效电阻,在一个时钟周期内,把 φ1 侧的电荷 φ2 侧,那这个搬移的电荷恰好就是 ΔVC,这样就得到了一个频率 F=1/T 决定的 SC 电阻,R=1/(FC)

C(Vφ1−Vφ2)=IT→R=(Vφ1−Vφ2)/I=1/(FC)

那么 VF 的电压为

VF=VDD×RREF+CRFOUTNDIVRREF=1+CRFOUTRREFNDIV1

在环路作用下,VREF=VF,这样得到

RREFCRFOUTNDIV=x1→FOUT=RREFCRxNDIV

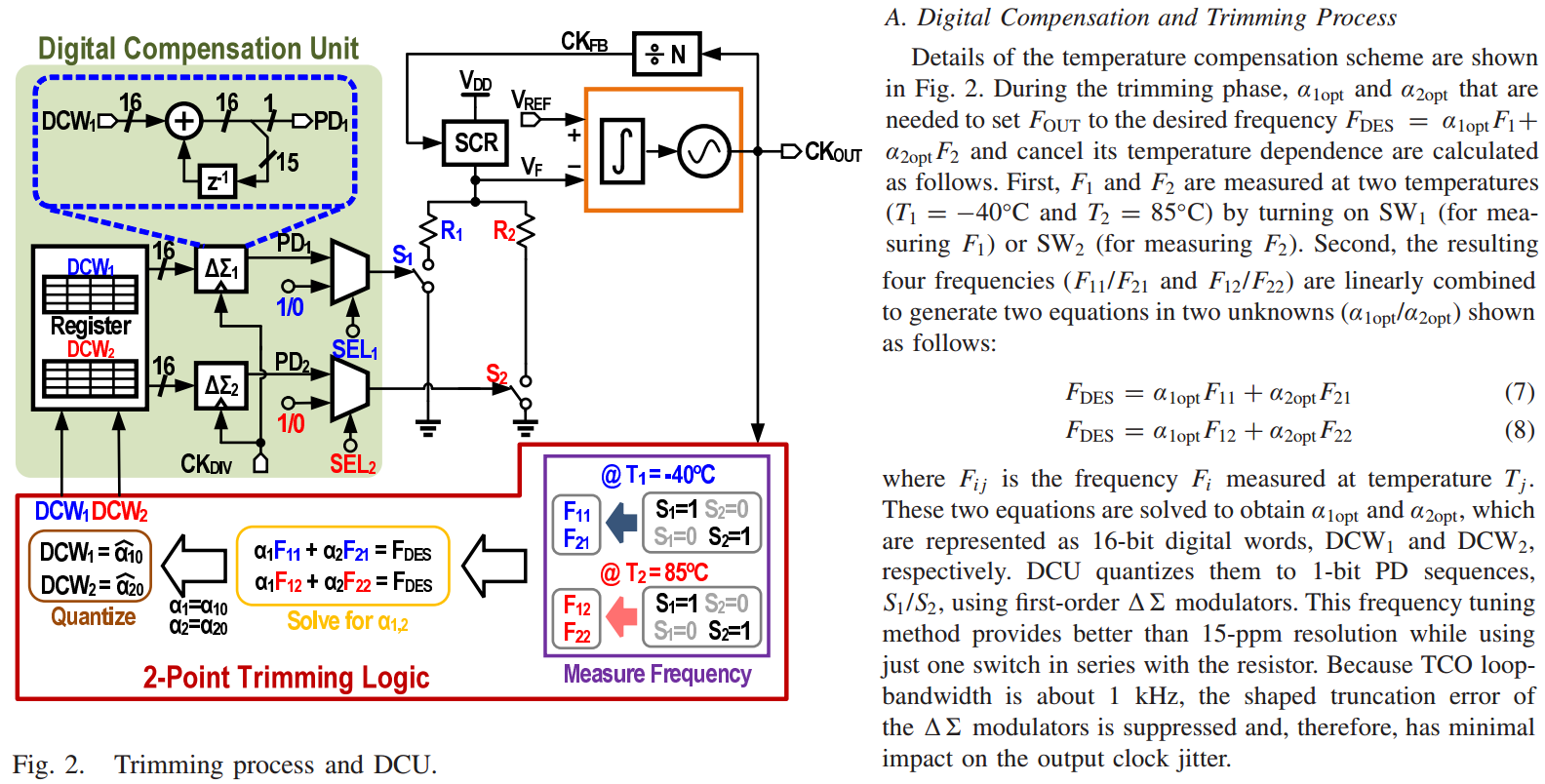

接着观察 RREF,其是由 Pulse Density Modulated 开关调制的,比例分别是 α1 和 α2,由于其是并联关系,用导纳表示更方便,得到

RREF1=R1α1+R2α2

那么最终的频率可以表示为

FOUT=α1R1CRxNDIV+α2R2CRxNDIV

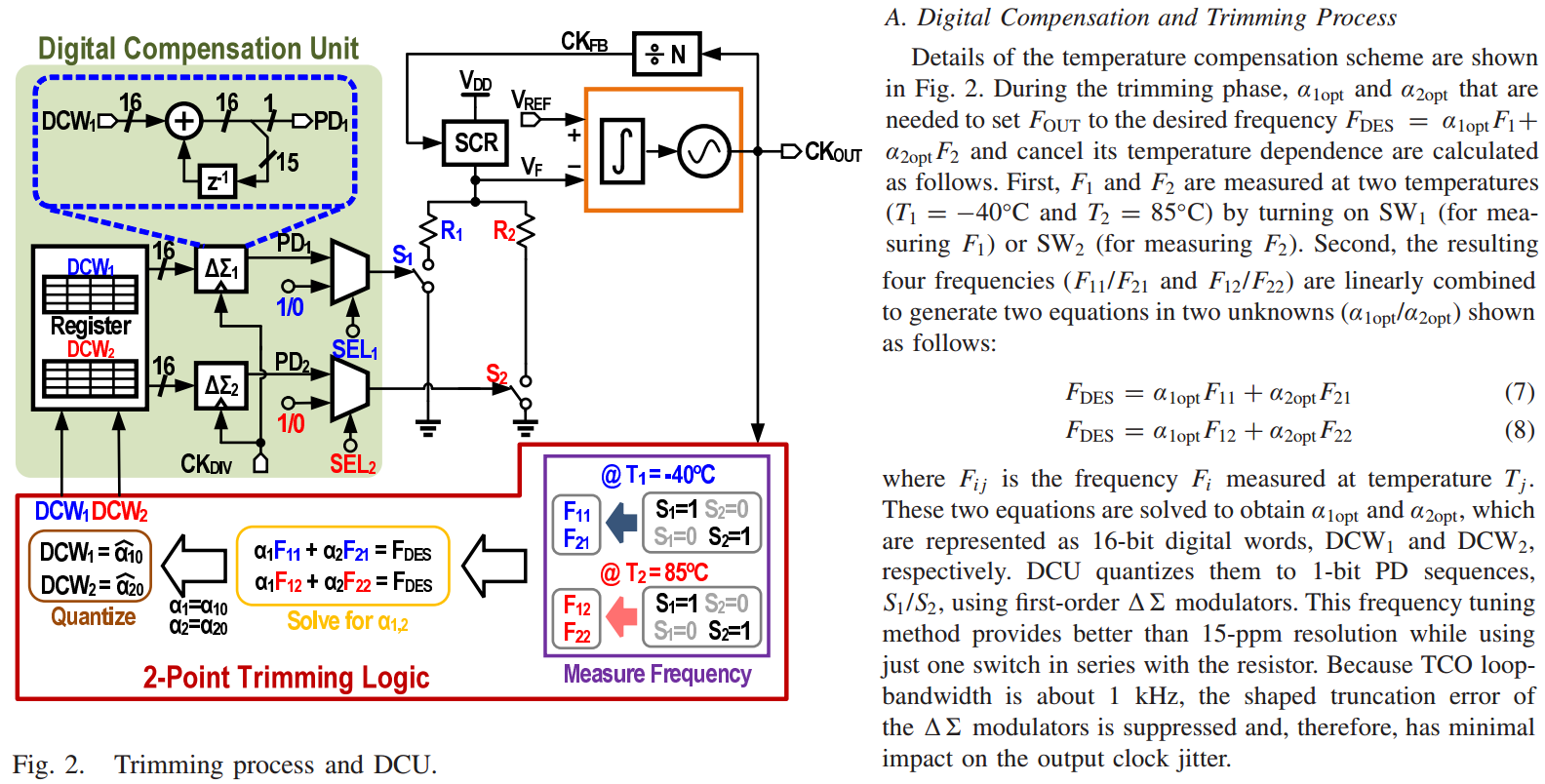

这样,就可以用 x 修调绝对精度,用 α1 和 α2 修调温度系数,修调的具体过程如下

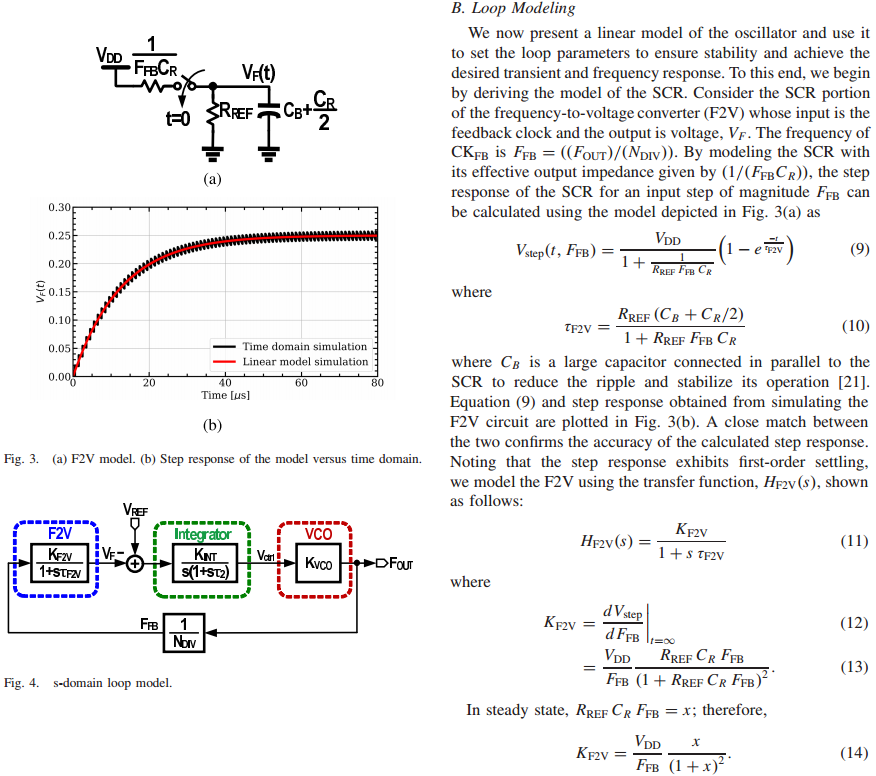

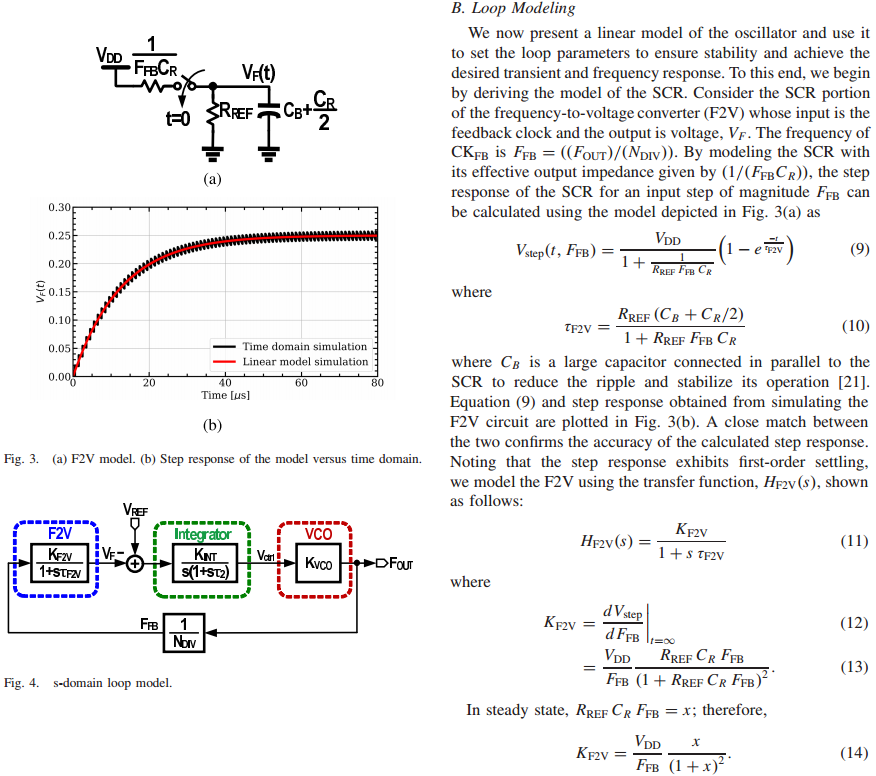

F2V 也就是前面的这个 SCR 结构,为了降低 Ripple,使其更加平均更能符合 Linear Model,在其后面增加了 CB 电容;然后写出了其阶跃响应函数,但是这个 “阶跃” 函数中,时间常数 τ 和前面的 “终值电压” 中都含有频率 FFB=FOUT/NDIV,为了求 “终值频率”;受限通过 VSTEP 的表达式,我们知道了这是一个一阶低通过程,这样其 s 域必然满足 KF2V/(1+sτF2V) 的形式,通过求导的方式得到 KF2V

INT 接着这里简化成了一个包含次级点 τ2 的积分器,接着得到 VCO 的增益以及后面的分频比,最终得到开环传递函数

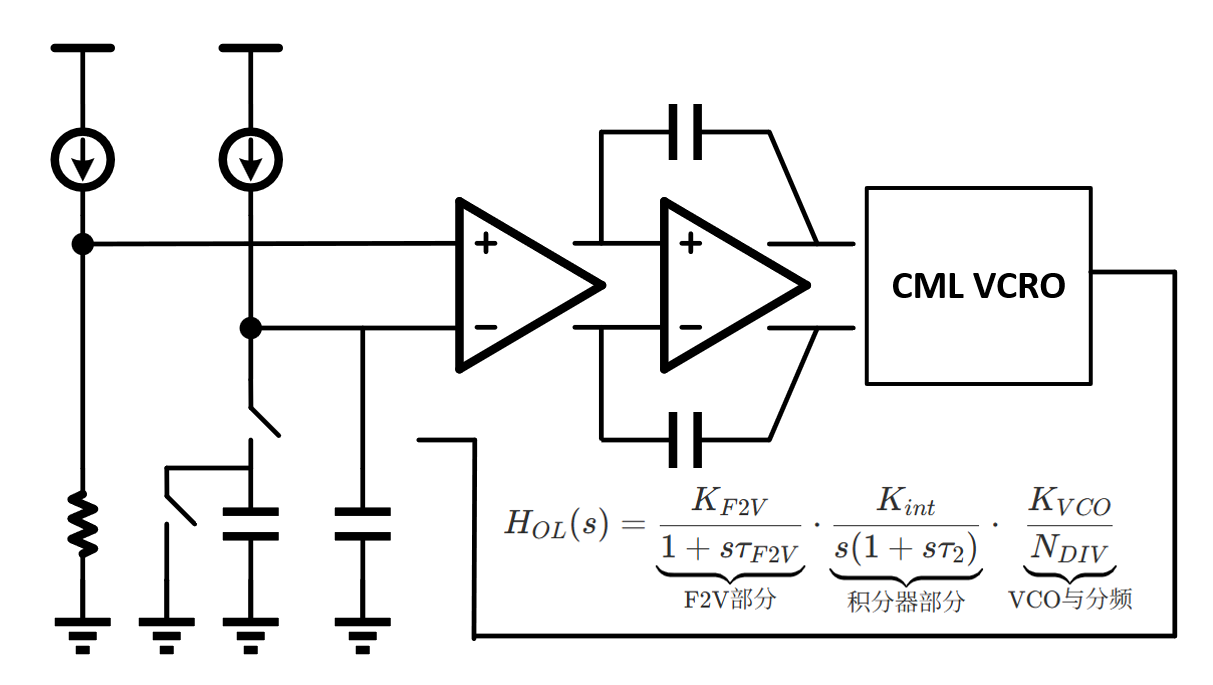

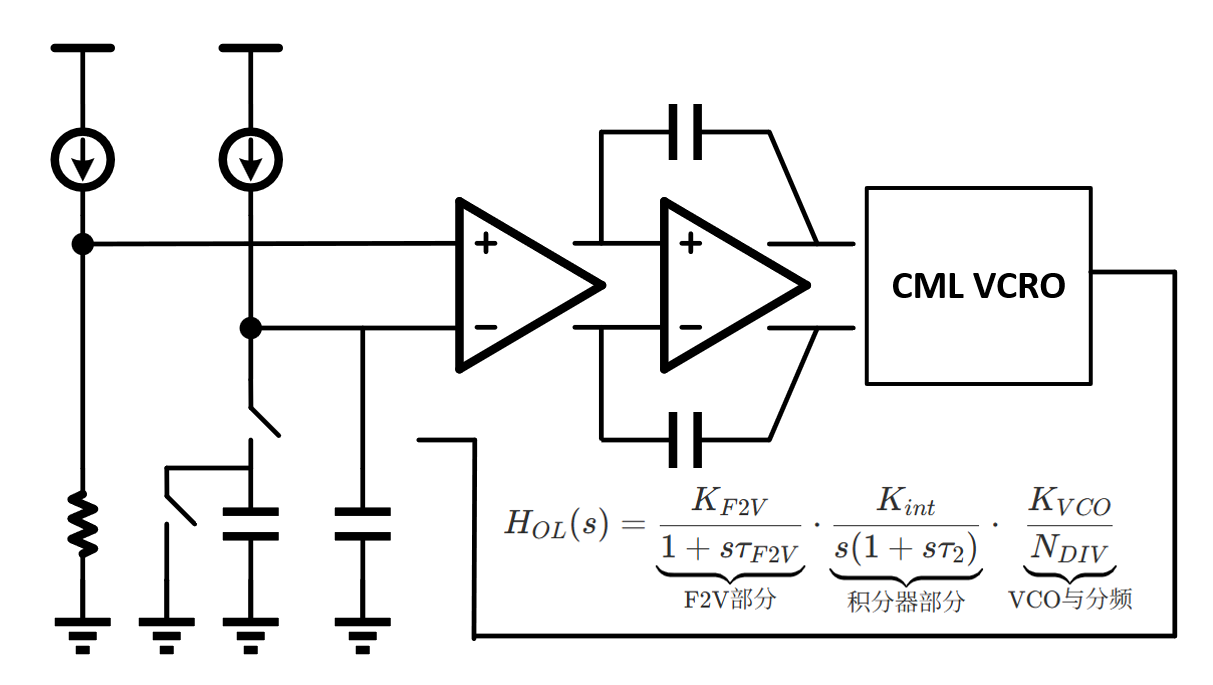

HOL(s)=F2V部分1+sτF2VKF2V⋅积分器部分s(1+sτ2)Kint⋅VCO与分频NDIVKVCO

当频率接近 ωu 时,ωu≪1/τF2V 且 ωu≪1/τ2。这样得到

ωu⋅NDIVKF2V⋅KINT⋅KVCO=1⇒ωu≈NDIVKF2VKINTKVCO

这里的 KINT=Gm/CINT,并不是积分器放大器的 DC 增益,敲好就是二级放大器中的输入管 gm 和 米勒电容 的比值

如下是一种变形

- SCR 与 RES 的分压,不再是对 VDD 的分压,而是使用 电流源/电阻 的形式;这样的优势在于与电源解耦,但是问题在于噪声会大?

- 使用差分的 CML VCRO 的优势仍然是与电源轨解耦,问题是更加复杂噪声偏大?

同样对比闭环的 VAF- Relaxation-OSC:

- 主要优势在于将 Comparator 替换成了 VCRO,同时利用 Frequency Divider,在 Charge Pump(充放电)这个环节的 Reference Frequency 可以更低,从而实现更低的功耗;其代价在于环路稳定性和启动时间(环路带宽);

- 首次的启动时间问题,或可通过复位积分器 / VCO 的初始 Control 尽可能接近稳定状态来解决;

- 问题解决到最后,解决了 R 的温度系数,充放电环节(SCR也好,还是Charge Pump 也罢)开关的非理想特性会是最后的难点