¶ 1 准备文件

数字会提供以下仿真文件(示例):

| Simulation Files | Description |

|---|---|

| /BIN_SCAN/dbg_master_scan.v | 最基本的dbg_master,导入到cadence, |

| /BIN_SCAN/scan_task.v | 被dbg_master调用的task |

| /BIN_SCAN/stimulus.v | SCAN仿真的激励 |

| /BIN_SCAN/scan_sdin_input.txt | SCAN输入数据 |

| /BIN_SCAN/scan_drdy_output.txt | 预期SCAN输出数据,用于与真实仿真输出XOR |

数字同时提供以下网表文件(示例)

| Netlist Files | Description |

|---|---|

| /NETLIST/xxx_dig_top_enc.v | 数字门级网表 |

| /NETLIST/tcb018bcdgp2a.v | VERILOG形式的数字标准单元库 |

| /NETLIST/xxx_dig_top_tc.sdf | 记录延迟信息的SDF反标文件 |

¶ 2 仿真流程

最简单的,是直接在cadence中GUI界面仿真:

- 首先创建dbg_master_scan的cell,创建一个verilog(functional)的cellview,复制.v文件,check save后生成symbol,注意替换绝对路径

include("/绝对路径/scan_task.v")和include("/绝对路径/stimulus.v") - 替换scan_task.v中的绝对路径,示例

$readmemb("/绝对路径/scan_sdin_input.txt")和$readmemb("/绝对路径/scan_drdy_output.txt"), - 替换stimulus.v中的绝对路径

$fopen("/绝对路径/xor_scan_output.txt") - 在数字门级网表xxx_dig_top_enc.v中,手动

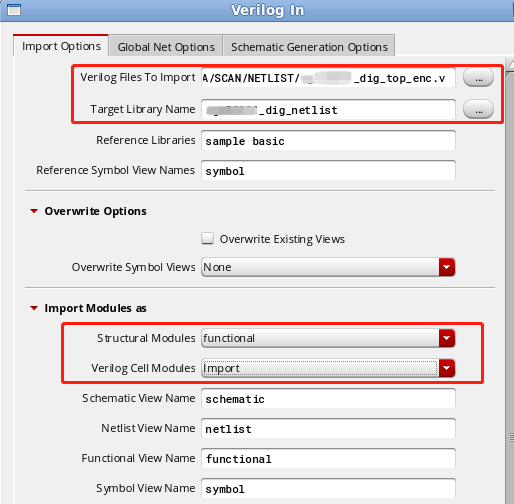

incldue "/绝对路径/tcb018bcdgp2a.v",然后开始导入流程,在cadence的CIW中,File → Import → Verilog,按照以下设置导入文件,注意Structural Module = Functional, Verilog Cell Modules = Import,最好导入到新创建的库

- 导入后,在xxxdig_top的functional cellview中最后,增加反标命令,其中xxx.log可以带上绝对路径,如果不带的话,xxx.log会在仿真器的网表路径下/simulation/…./ams/config/netlist/xxx.log

module xxx_dig_top();

...

...

initial begin

$sdf_annotate("/绝对路径/xxx.sdf",,,"xxx.log","MAXIMUM");

end

endmodule

- 之后按照标准的AMS流程仿真,最好将与SCAN模式相关的pads_top替换成门级网表进行仿真。输出的XOR结果全为0,则表示结果是正确的。

¶ 3 Debug

在xrun.log或者xxx.log中报一下warning可能并不是致命错误(有待深入理解):

Unable to annotate to non-existent triming check….

这个问题不大,这个只是说没有查reset端的相关时序。应该不会影响仿真。Annotion resulted in a negative dely value or pulse limit to sepcify path or interconnect delay…

仿真器会把负数处理成0

之前存在收敛风险但最终仿真成功的verilogams模型,可能在进行数字门级网表+SDF反标DELAY仿真时不再收敛。本质还是模型写得有瑕疵,将real型的变量传递到electrical节点时,一定注意这个real型的变量有初值,最好在initial中给一个初值,always@(*)无法真正赋予变量初值,容易造成收敛错误。

¶ 4 sdf_annotate()

$sdf_annotate(SDF_FILE, INSTANCE_PATH, SDF_SETUP_HOLD_CHECK, LOG_FILE, SDF_DELAY_TYPE, SCALE_FACTORS, CONSTRAINT_FILE);

- SDF_FILE:SDF文件的路径及名称,必须指定。

- INSTANCE_PATH:实例化的层次路径(可选)。如果没有指定,则对当前层次的所有模块进行标注。

- SDF_SETUP_HOLD_CHECK:检查 setup/hold 时间的标志(可选)。值为

1或0,默认值为1(开启)。 - LOG_FILE:日志文件的路径及名称(可选)。

- SDF_DELAY_TYPE:延迟类型(可选)。可以是

"MINIMUM"、"TYPICAL"或"MAXIMUM",用以选择 SDF 文件中的哪种延迟值进行仿真。 - SCALE_FACTORS:用于调整延迟值的比例因子(可选)。通过指定比例因子,可以缩放延迟值,常见格式为

("1.0", "1.0", "1.0"),对应缩放MINIMUM、TYPICAL和MAXIMUM延迟值。 - CONSTRAINT_FILE:约束文件的路径及名称(可选),包含时序约束信息。

$sdf_annotate("design.sdf", u_top, 1, "design.log", "TYPICAL", ("1.0", "1.0", "1.0"), "constraints.sdf");

这个语法示例表示,将 design.sdf 文件中的延迟信息加载到 u_top 实例化模块中,开启 setup/hold 时间检查,日志记录到 design.log,使用 TYPICAL 延迟,延迟值不缩放,并加载 constraints.sdf 中的时序约束信息。

通过 $sdf_annotate,你可以确保在仿真中考虑到综合后的时序信息,从而获得更精确的仿真结果。

¶ 5 SDF 文件

在SDF文件中,延迟信息通常会按照不同的条件进行分类,分别表示最小延迟(MINIMUM)、典型延迟(TYPICAL)和最大延迟(MAXIMUM)。这些延迟值是在不同工艺角(corner case)下测量得到的,用来反映电路在不同条件下的性能。

¶ 5.1 查看SDF中的信息

要知道SDF文件中分别对应的MINIMUM、TYPICAL和MAXIMUM延迟信息,可以查看SDF文件中的延迟标注部分。SDF文件通常由多个块组成,每个块都可能包含以下几个部分:

- (IOPATH ...):表示输入到输出路径的延迟。

- (INTERCONNECT ...):表示模块之间的连线延迟。

在每个延迟条目下,通常会提供三组数据,对应MINIMUM、TYPICAL和MAXIMUM三种延迟值。

¶ 5.2 典型的SDF语法示例

(DELAY (ABSOLUTE (IOPATH (posedge CK) (posedge Q) (1.0:2.0:3.0)) (IOPATH (negedge CK) (negedge Q) (0.9:1.8:2.7)) (INTERCONNECT U1/A U2/B (0.5:1.0:1.5)) ) )

在这个示例中:

- DELAY:表示延迟块,SDF文件中的主要部分之一。

- ABSOLUTE:表示延迟是绝对值(而不是增量值)。

- IOPATH (posedge CK) (posedge Q):表示从时钟信号

CK上升沿到输出Q上升沿的延迟路径。 - (1.0:2.0:3.0):表示该路径的延迟值,三个数字分别对应 MINIMUM、TYPICAL 和 MAXIMUM 延迟。

- 1.0:最小延迟(MINIMUM)。

- 2.0:典型延迟(TYPICAL)。

- 3.0:最大延迟(MAXIMUM)。

在另一个路径中:

-

(0.9:1.8:2.7):同样表示从

CK下降沿到Q下降沿的延迟值,分别为最小、典型和最大延迟。 -

(INTERCONNECT U1/A U2/B (0.5:1.0:1.5)):表示模块

U1的端口A到模块U2的端口B之间的连线延迟,分别对应最小、典型和最大延迟。

¶ 5.3 如何选择对应的延迟类型

在Verilog仿真中,通过 $sdf_annotate 的第五个参数可以选择使用哪种延迟类型:

"MINIMUM":选择SDF文件中的最小延迟值。"TYPICAL":选择SDF文件中的典型延迟值。"MAXIMUM":选择SDF文件中的最大延迟值。

¶ 5.4 小结

通过查看SDF文件中的延迟条目(如 IOPATH 或 INTERCONNECT),你可以看到三组数字,分别表示最小、典型和最大延迟值。这些值可以在时序仿真中通过 $sdf_annotate 指定的延迟类型进行选择,以反映不同条件下的时序行为。