¶ 1. 准备工作

¶ 1.1 Cadence设计环境

(1)输入 virtuoso & 后,Cadence将缓慢打开,请保持耐心直到其后台程序运行完毕。

首先你可能会看到两个窗口,一个窗口是 What‘s new(这个可能没有),这个窗口是IC617的版本更新简介,你可以通过以下方式永久地关闭它:菜单栏左上角 File | off at startup。

另一个窗口标题为 Virtuoso 6.1.7 ,这个是命令交互窗口( CIW , Command Interpreter Window)。

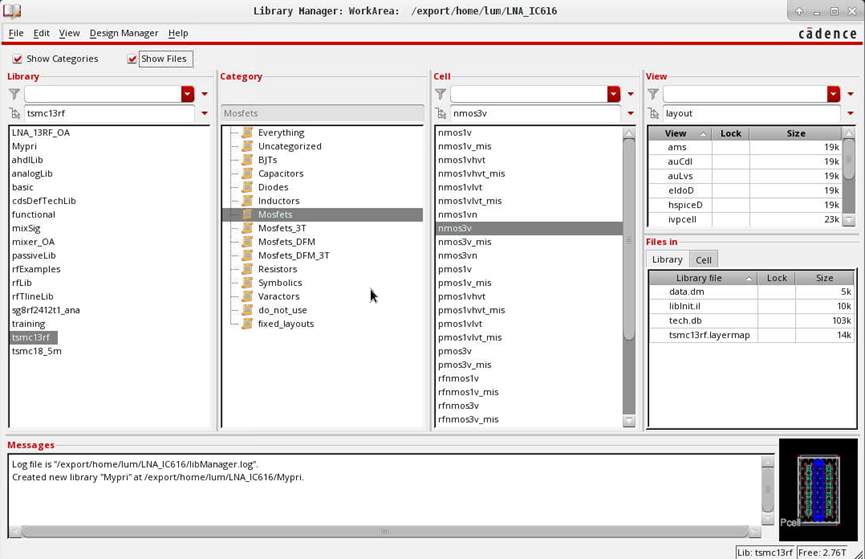

(2)单击菜单栏 Tools | Library Manager,你将看到下图所示界面。

(3)在 Library 栏下,工艺库和我们的工程库都在这里。其中Cadence自带的仿真库有:ahdlLib, analogLib, basic, functional, rfLib… 这些库提供了大量的仿真元器件,甚至包括运放,滤波器等元件,可以实现自顶而下的设计的设计流程,即利用这些元件搭建系统结果,制定各个模块的参数,再逐一设计模块电路。

(4)通过勾选 Show Category ,你将看到 Category 栏,我们可以通过这一栏将库中大量的文件分目录整理。

(5)在Cell下,这是一个小型的设计单元,在这个设计单元下,你可以继续创建 schematic, symbol, layout, av_extracted, spectre 等Views文件。

¶ 1.2 添加工艺库文件

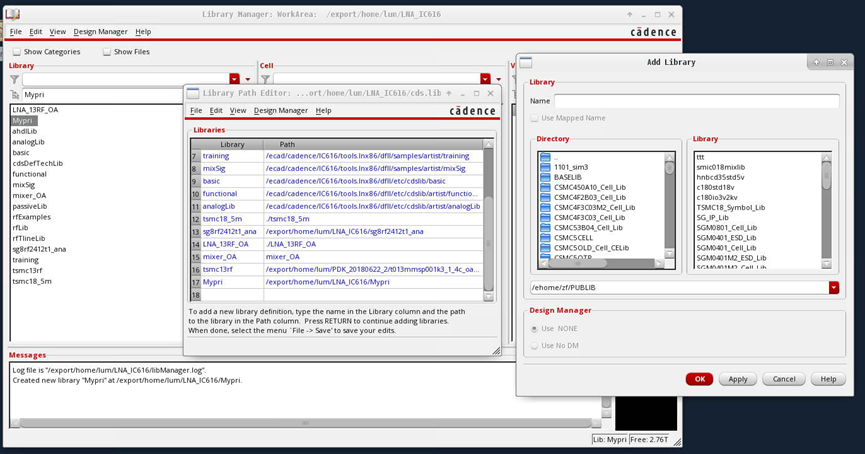

在 Library Manager 窗口下,Edit | Library path,你将看到所示的窗口,接着 Edit | Add Library,Directory选择到工艺库安装的目录,即可以在 Library 栏下看到相应的工艺库。

找到统一放置PDK的文件目录,选择到相应的工艺、金属层数的文件目录下,即可以在Library栏下看到相应的工艺库。

最终在添加时,注意在 Library Path Editor 窗口中保存,File | Save,最后在 Library Manager 窗口中,View | Refresh。

¶ 2. 原理图编辑

¶ 2.1 建立工程Library和原理图View

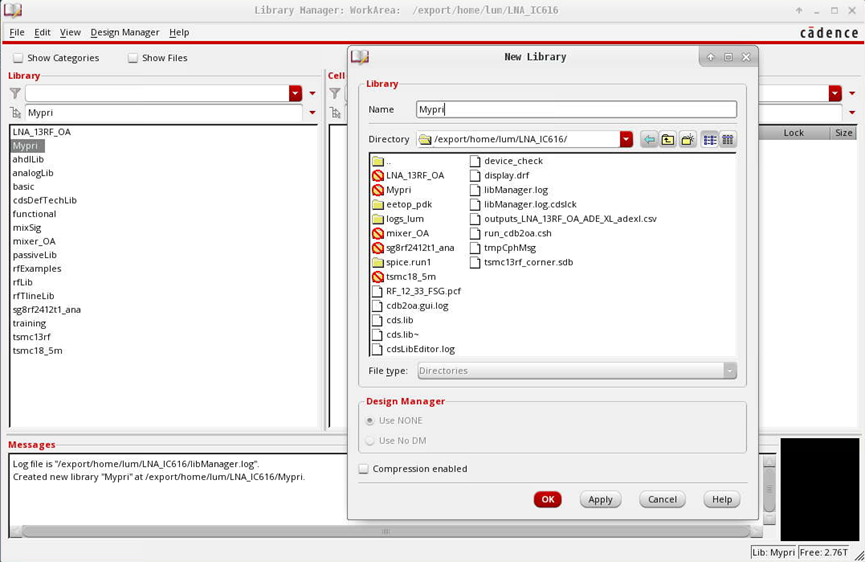

(1)在Library Manager窗口中,File | New | Library

(2)在弹出的New Library窗口中,Name栏输入MyPrj,点击”OK”

(3)在弹出的 Technology File for New Library 窗口中,选择Attach to an existing technology library,点击OK

(4)在弹出的 Attach Library to Technology Library 中,选择 tsmc13rf,点击 OK

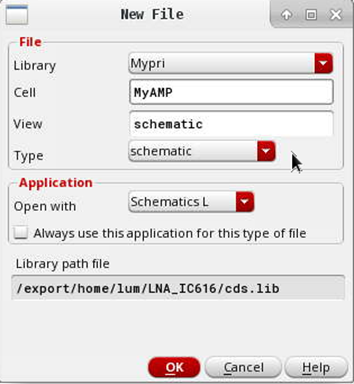

(5)在 Library Manager 窗口中的 Library 栏中,选中刚才创建的 MyPrj ,然后依次单击File | New | Cell View,在弹出窗口中Cell栏中MyAMP,Type选择为schematic,单击OK,接下来会弹出 schematic L 的原理图编辑窗口

¶ 2.2 绘制原理图

(1) 按下 I 键,在弹出的 Library 窗口下,依次选择 Library | Category | Cells | Views ,选中相应器件的 Symbol,选中相应器件的 Symbol,然后单击 Schematic L 窗口的空白处,即可添加器件。

(2)选中 Schematic L 已添加的器件,按下 Q 键,即可以编辑器件参数,参数可以用用变量名表示,之后我们可以在仿真窗口中设置相应的Variable,即可以快速修改参数进行仿真。

(3)按下 W 键,可进行导线绘制,通过按下滚轮中键,我们可以绘制出斜线。

(4)按下 L 键,可以更改连线的线网名,简化原理图。

(5)按下 P 键,可以添加端口 Pin,建立相应的 Symbol,实现模块化设计。

(6)按下 N 键或 shift+N 键,可以添加注释文本或注释形状。

(7)选中一个 symbol,shift+E 进入子电路,ctrl+E 退出自电路。

(8)选中一个器件,按下 R 键,旋转相应器件。通过图标,可以选择旋转方式。

(9)按下 F 键,使设计图适应当前窗口大小。

(10)按下鼠标中键,拖动显示中心点。

(11)按下 U 键,撤销上次操作。

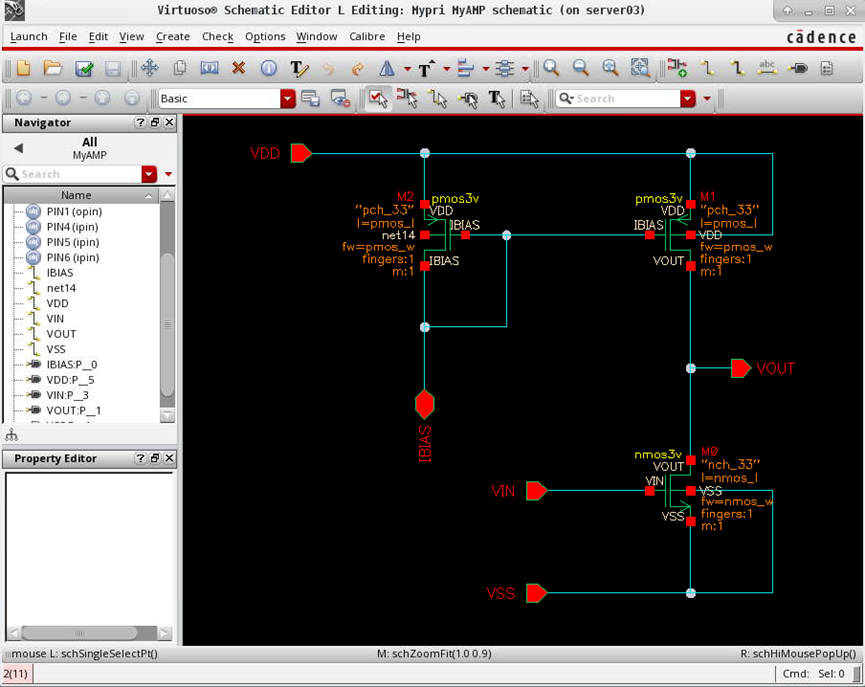

通过以上快捷键,我们可以迅速的画出以下原理图

-

M1, M2: tsmc13rf-pmos3v Length=pmos_l, Finger width=pmos_w

-

M0: tsmc13rf-nmos3v, Length=nmos_l, Finger width=nmos_w

(这里的器件参数,可以用实际的数值表示,也可以用变量名表示,用变量名表示可以方便地进行调试仿真)

¶ 2.3 创建Symbol与Test Bench

通常,我们将一个相对独立的电路模块打包成一个 Symbol ,配置好相应的I/O端口。仿真时,建立一个相应的Test Bench,将实际器件(如nmos1v, poly resistor)与仿真模拟器件(如vdc, port, vccs)尽可能分开。

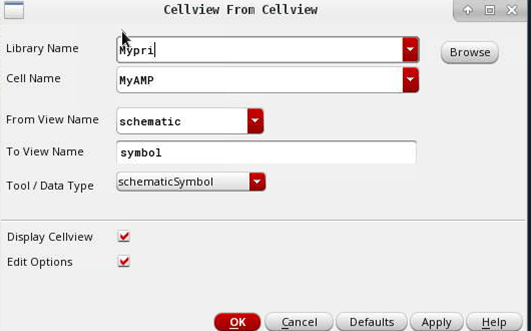

(1)Symbol 的建立方法是,首先为当前的模块电路配置好相应的 PIN,然后在原理图编辑窗口点击 Create | Cell View | From Cell View,在弹出的窗口点击 OK 。

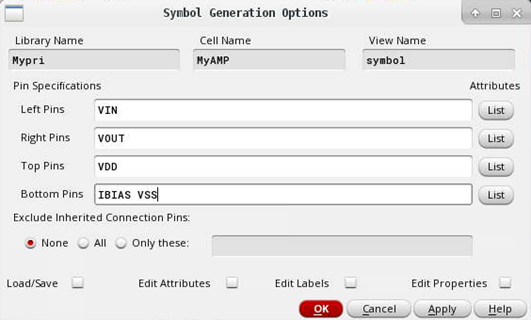

(2)然后在 Symbol Generation Options 的窗口调整PIN的位置,点击 OK。

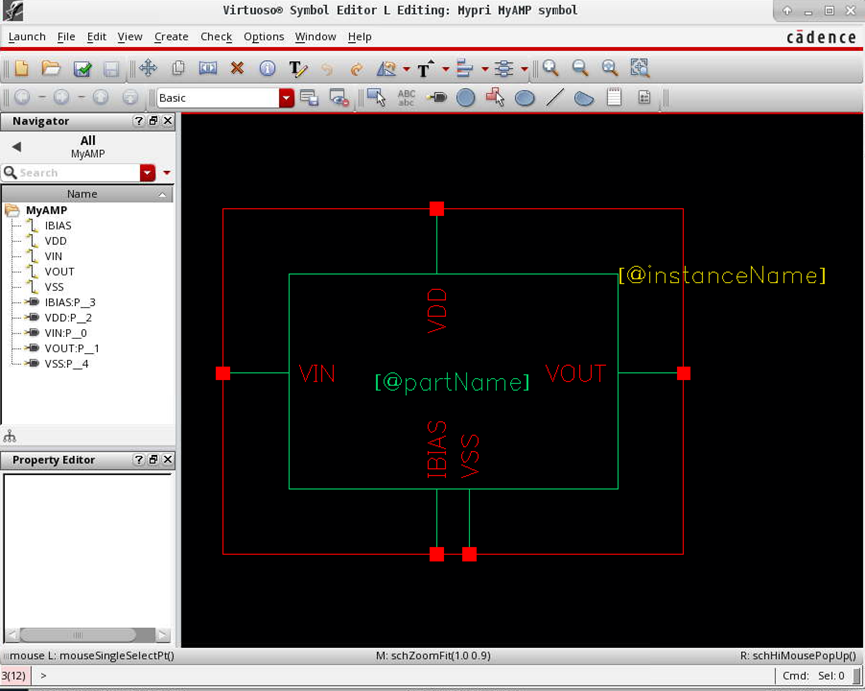

(3)最终会创建以下 Symbol ,保存关闭即可。

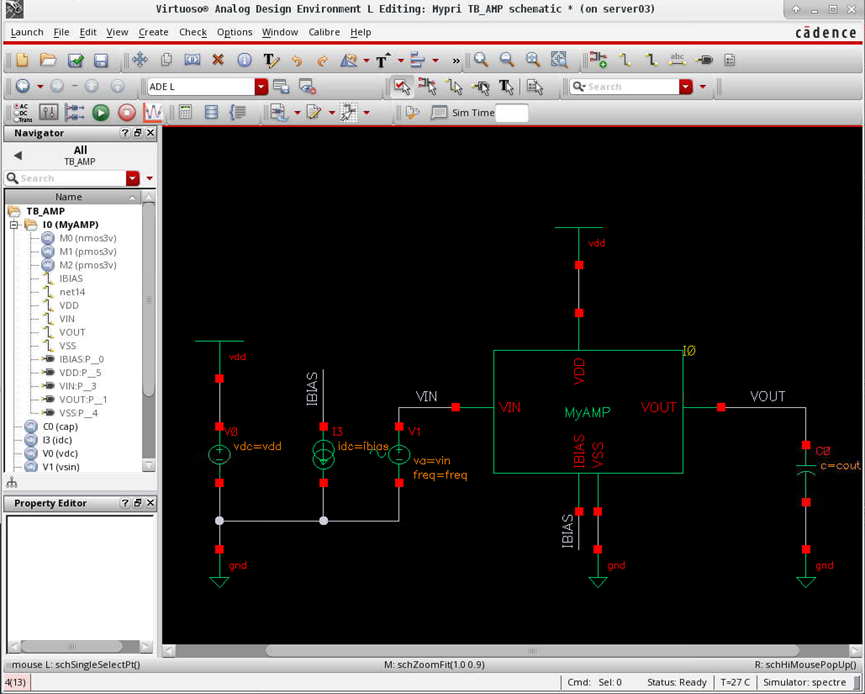

(4)建立新的 Schematic 如下,名称为TB_AMP

- V0: analogLib-vdc, DC Voltage=vdd

- I3: analogLib-idc, DC Current=ibias,

- V1: analogLib-vsin, DC Voltage=vref, AC magnitude=1V, Amplitude=vin, Frequency=fre

- C0: analogLib-cap, capacitance=cout

(这里的器件参数,可以用实际的数值表示,也可以用变量名表示,用变量名表示可以方便地进行调试仿真)

¶ 2.4 Schematic L的便捷功能

相比Cadence IC5,Cadence IC6的原理图编辑页面人性化了许多,给设计者创造了更为高效便捷的设计环境,这里笔者仅介绍常用的几个功能:

(1)便捷的 Annotation 管理:在 Schematic L 窗口空白处,单击右键 | Annotation ,可以自由的配置标注信息,让原理图不再混乱。

(2)Navigator 的运用:在 Schematic L 窗口的菜单中,Windows | Assistance | Navigator,我们可以打开导航窗口,在第一下拉菜单中,我们可以选择 All, Cells, Instance, nets 等,我们即可以在下方的列表中快速地找到相应的器件,线网,甚至是某一个模块,相比于 Edit | Search方便很多。

(3)Property Editor 的运用:通常我们编辑和观察器件参数时,是通过 Q 键完成的,但是通过Windows | Assistance | Property Editor,我们可以便捷地观察器件参数,无需再去 QQQ 。

(4) Select Filter 的运用:快捷键 Ctrl+F ,可以打开 Select Filter ,这样我们在圈选,点选时,只会选取我们指定的目标类型。

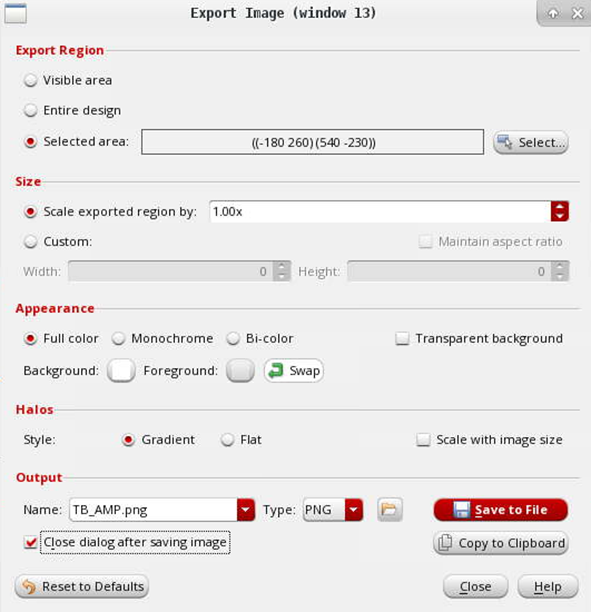

(5)Export image 功能:在原理图编界面,File | Export Image

- Export Region 的三个选项,按需选择,若选择 Selected area ,返回到Schematic中框选一片区域,之后 Selected area 后面的方框中就会出现所选区域的坐标信息。

- Size 选择X1,最终的输出图片与当前Schematic的缩放大小一致。

- Appearance,Halos 按需选择。

- Output 中,选择图片格式,点击文件夹图标(在Save to File 左侧),选择图片输出目录,最后点击 Save to File 即可。

¶ 3. ADE L仿真

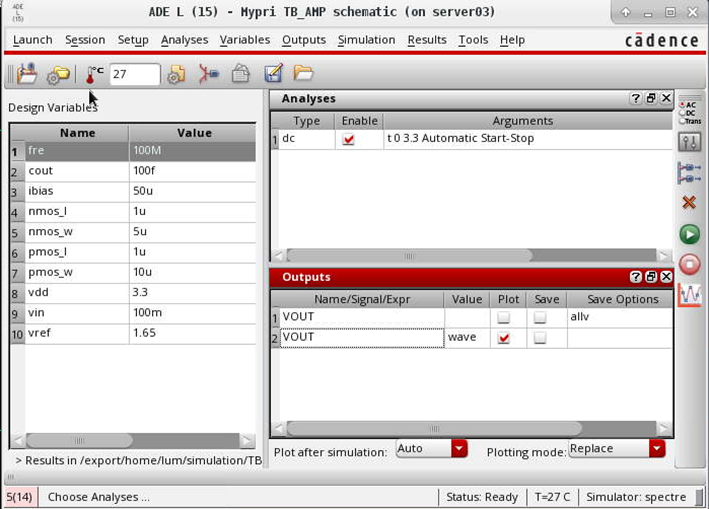

在原理图界面下,Launch | ADE L 即可以启动 Analog Design Environment L ,在 Analog Design Environment L 窗口下,Variable | Copy from Cellview,然后依次输入响应的参数。

¶ 3.1 DC分析

¶ 3.1.1 基本流程

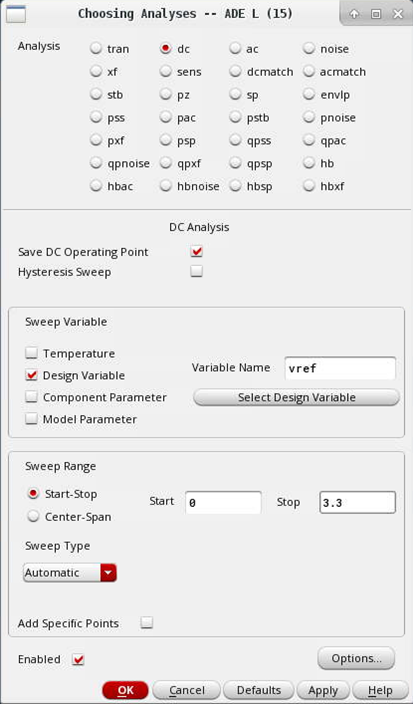

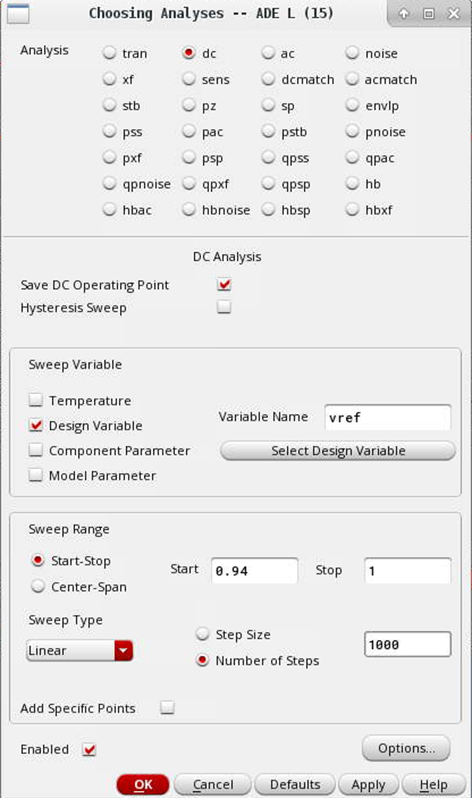

(1)首先我们要找好直流工作点,Analysis | Choose,然后按照下图配置。Outputs | To be Plotted | Selected on Design,点击 VOUT 线网。

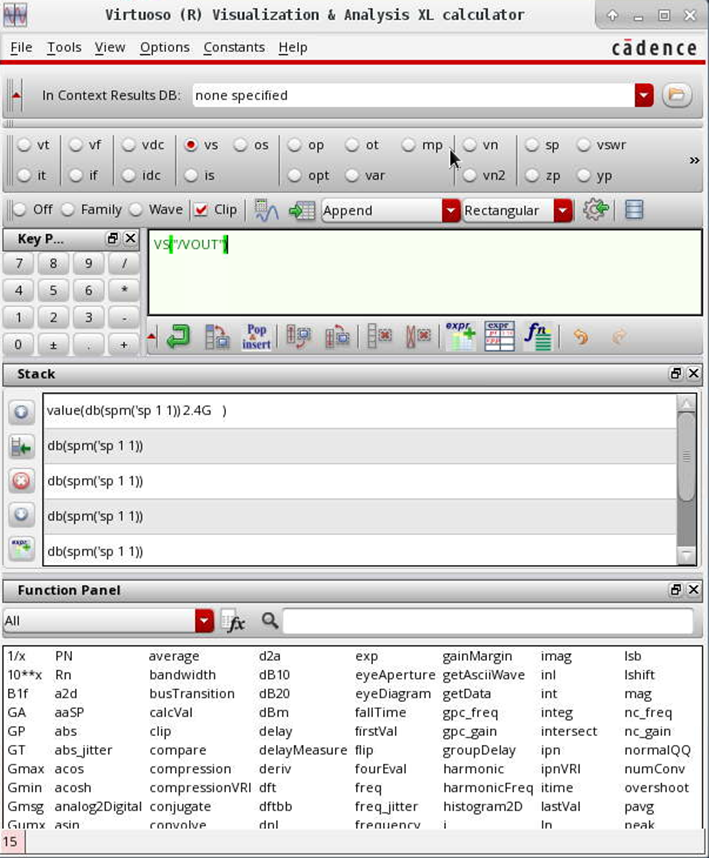

(2) 这里我们通过 Calculator 来添加输出,Tools | Calculator,然后点击圆圈选项 vs ,之后弹出原理图界面,点击VOUT线网,这样一个 VS(“/VOUT”) 的公式就编辑好了,这个公式的意思是获取DC扫描分析的数据。至于其它,将鼠标放置在 vt,it,vf… 上面,可以看到其相应的功能。

在Function Panel 中,提供了非常多的函数,这些函数在工作学习中,非常重要,在后续的介绍中,笔者也会穿插介绍一些函数的使用。

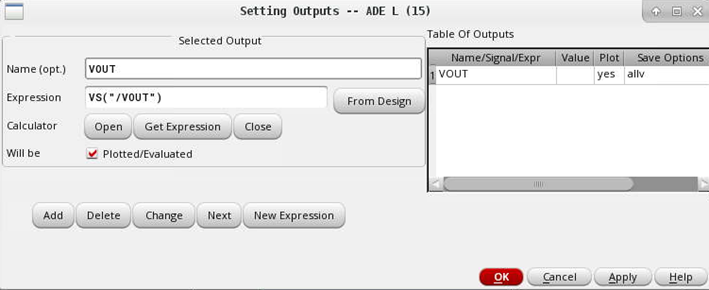

(3)我们将这个窗口放在一边,不要关闭,返回到ADE L窗口,点击Outputs | Setup,然后在弹出的窗口点击Get Expression,就把Calculator中的表达式复制过来了,然后在 Name 栏中写上任意名字,如 VOUT 。

(4)最终,我们的ADE L的窗口应该看起是这个样子。

(5) 然后点击绿底白三角按钮进行仿真或者 Simulation | Start。注意要对原理图及其子电路进行 check and save ,确保没有错误后,才能进行正确的仿真。之后会弹出波形窗口。

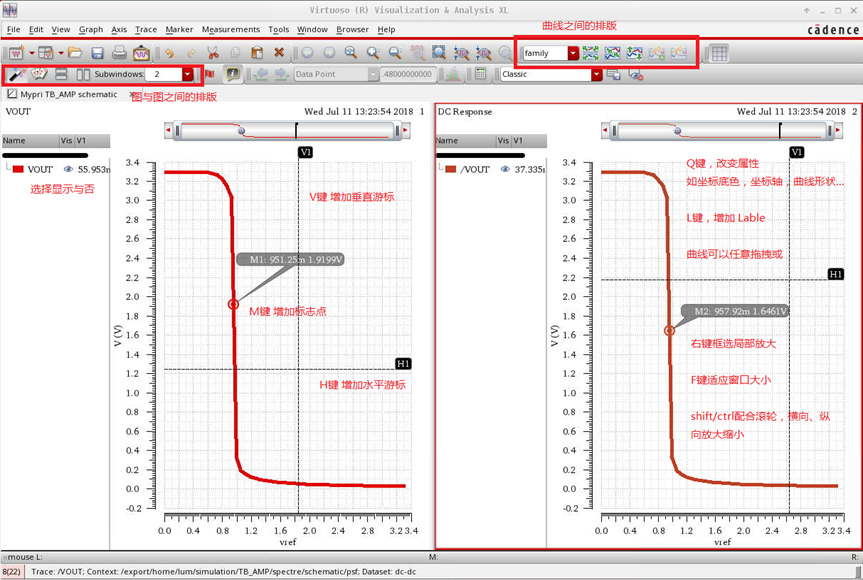

该窗口提供了非常方便的图像查看窗口,下图中的红字仅提供了一些简单操作技巧,更多的技巧请自己探索。

¶ 3.1.2 扫描精度

(1)通过直流分析,我们发现当输入从0.92V变化到0.99V时,输出从3V变化到了0.3V,放大器在这一区间具有很高的增益,因此我们将直流工作点放在0.95V。

这样的结果往往是错误的,因为我们在进行DC扫描分析的区间是0-3V,这是一个非常大的区间,而且我们在 sweep type 选择 automatic ,这样仿真器可能仅选择了几十个点,大致描绘出了输出-输入的波形,而在具体的放大区,其实并不准确,因此,我们重新配置DC analysis如下图所示。

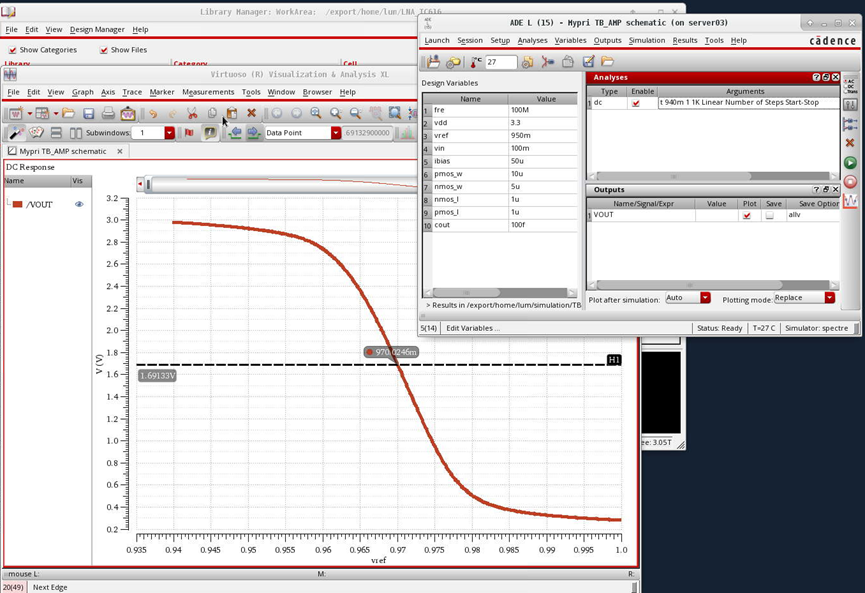

(2)在ADE L窗口,我们删除掉添加的两个输出,重新通过 Outputs | To be plotted 添加 VOUT输出,然后点击仿真,这样我们的ADE L窗口和最终的仿真结果为:

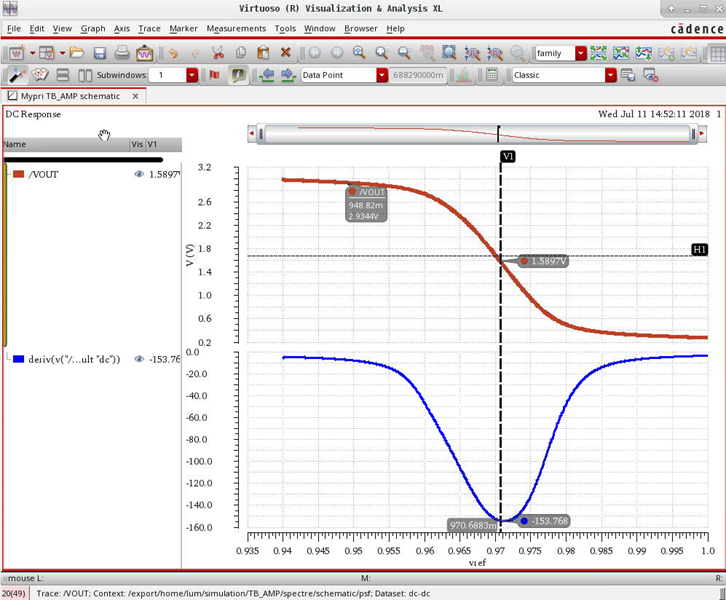

(3) 此时,我们可以通过对这条曲线求导,就可以得到放大器的增益,在波形显示窗口,Tools | Calculator,选择 wave,点击波形窗口中的曲线,这样 Calculator 窗口表达式的状态为:v(“/VOUT”?result “dc”) 。

(4)在 Calculator 窗口的 Functional panel 中找到 deriv 函数,单击 deriv ,然后点击 off family 一栏中的第五个按钮,一个计算器波浪线构成的图标,这样求导的结果就显出出来了。

(5) 通过对波形进行适当的整理,我们发现当输入为0.97V时,大约有-150倍的增益。

¶ 3.1.3 DC分析的扩展

(1) 在直流分析设置中,勾选 save dc Operating points ,可以用来观察电路的DC工作点,在ADE L窗口中 Results | Annotate | DC operating points,或仿真结束后,在原理图窗口空白处 右键 | Annotate | …

(2)在直流分析中,我们将一个电流源与一个电容串联,仿真器会报错,在ADE L窗口中 Simulation | Option | Analog 或者在在 dc analysis 设置中的 Option 选项,这里涉及到很多仿真精度,仿真近似的问题。例如,将一个1V的电压源与1F的电容串联,我们始终可以观察到有1pA的直流电流流入电容,改变电容的容值,1pA不改变,这是为什么?答案在 Option 中的 iabstol 。

在其它类型的仿真中,同样涉及到仿真精度的问题。

¶ 3.2 AC分析

¶ 3.2.1 基本流程

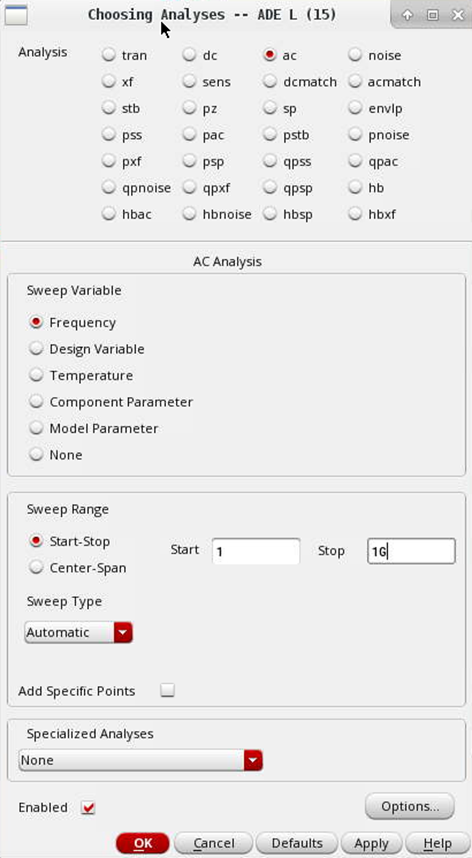

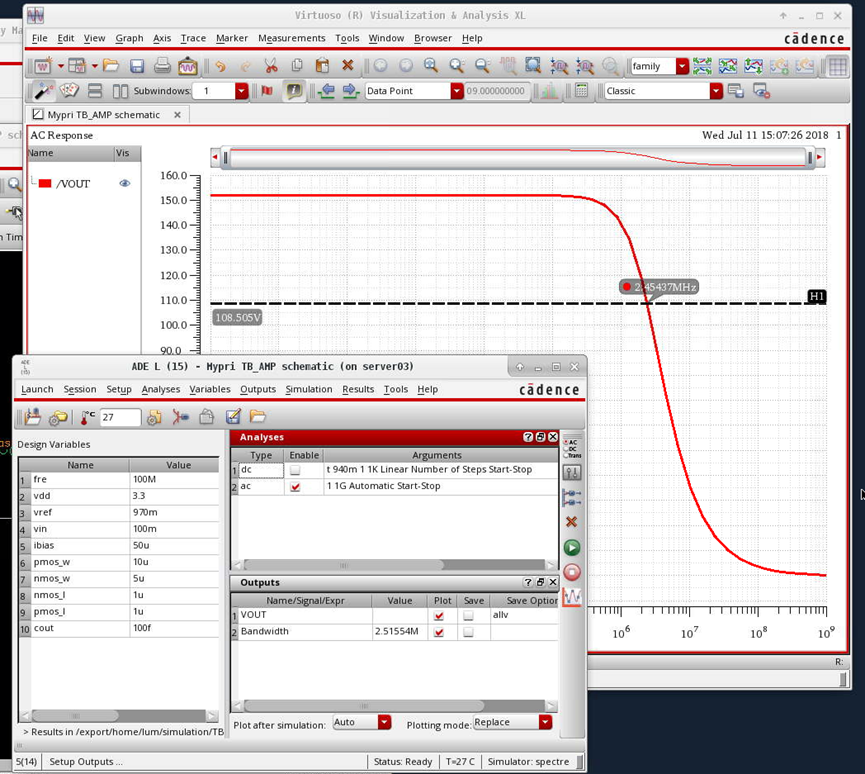

(1)更改变量vref=0.97,添加AC仿真,如下图配置。

(2)将ADE L窗口 Anaysis 栏的 DC 分析去除勾选。

(3)打开 Calculator ,利用 vf ,将 VOUT 输出获取到表达式窗口中,表达式的状态应为 VF(“/VOUT”) 。

(4)在 Calculator 的 Function panel 中找到 bandwidth 函数,左键单击 bandwidth ,然后不用更改默认配置,点击 OK ,这样表达式的状态应为 bandwidth(VF(“/VOUT”) 3 “low” )

(5)在 ADE L 窗口中,Outputs | Setup ,然后 Get Expression , Name 栏中填写 Bandwidth ,点击 OK ,这样最终的 ADE L 的面板为和波形结果为:

(6) 我们发现,AC增益为152,这与DC扫描求导的结果一致;增益下降为0.707倍时,表示带宽,这与Calculator中的bandwidth公式计算结果一致。

¶ 3.2.2 AC/DC仿真结果不可信

DC分析与AC分析,仅能作为参考,DC分析是为了观察电路的直流工作状态,没有交流信号的信息。AC分析是为了观察电路的频率响应特性,一旦确定了直流工作点,将按照小信号模型分析,不考虑直流特性。

作如下考虑,若我们将放大器偏置在0.97V,输入幅值为1V, 1MHz的正弦波,我们真能在输出点看到150V的的正弦波吗?若我们将放大器偏置在0.97V,输入幅值为1nV, 1MHz的正弦波,我们真能在输出点看到150nV的的正弦波吗?

答案是否定的,无论是DC还是AC,其仿真结果都具有片面性。接下来,我们将通过Transient仿真来回答上面两个问题。

¶ 3.3 Transient分析

¶ 3.3.1 基本流程

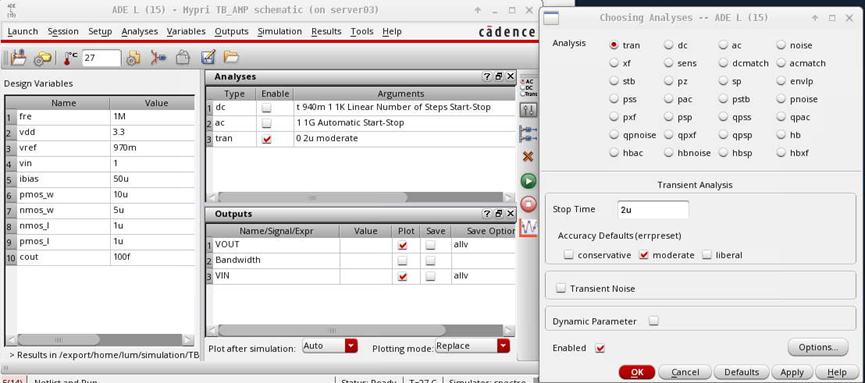

(1)在ADE L窗口中,更改vin=1,fre=1M,去除勾选ac分析,将 VIN 线网通过 to be ploted 增加到输出列表,同时增加 tran 分析,设置如下:

(2)点击仿真,结果如下。我们看到由于带宽是2.5M,我们选择了1M的信号,所以输出波形的变化与输出波形的变化时同步的,速度上完全没有问题,但是,由于有限的电源电压,发生了严重的截止失真。

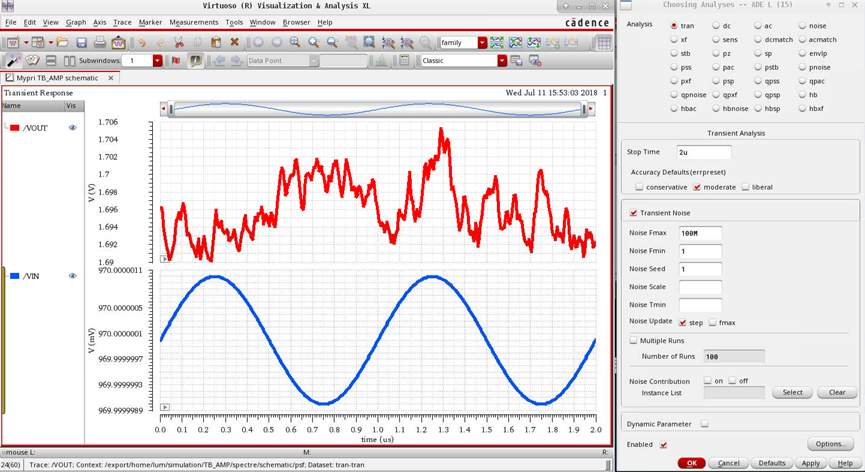

(3)在ADE L窗口中,更改vin=1n,fre=1M,去除勾选ac分析,将VIN线网通过to be ploted增加到输出列表,同时更改Transient分析,仿真设置与仿真结果如下:

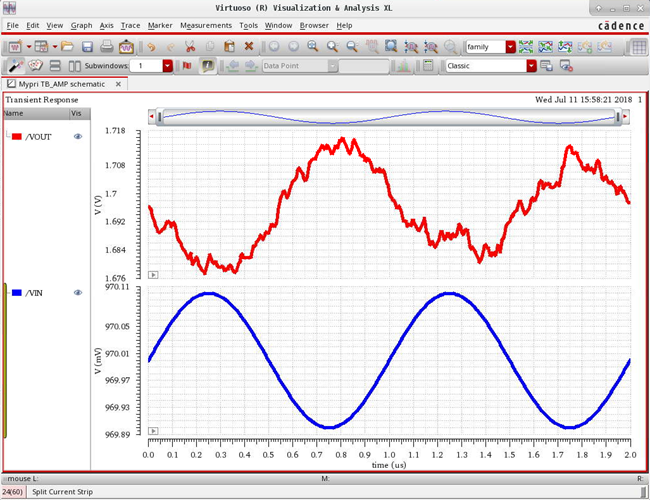

(4)我们发现,由于噪声的存在,运放无法分辨1nV的输入,本应150nV的输出信号完全被噪声淹没。我们重新设置vin=100u,这样放大器才能分辨出输入信号,在输出给予相应的反向放大,但是,同时也在遭受噪声的困扰。

¶ 3.3.2 Transient分析的扩展

(1)在仿真具有记忆特性的电路时,常常会遇到不收敛的问题。最简单的一个收敛错误的例子,一个1uA的idc与一个1uF的电容串联,然后进行1ms的Transient分析,仿真器报收敛错误。

这里,我们要给电路的某些节点设置 initial condition ,设置一个初始电压,以帮助进行收敛。设置方法是在ADE L窗口中,Simulation | Convergence aids | Initial Condition ,然后选择输入电压,点击原理图上要设置的线网,即可以为其设置初始电压状态。

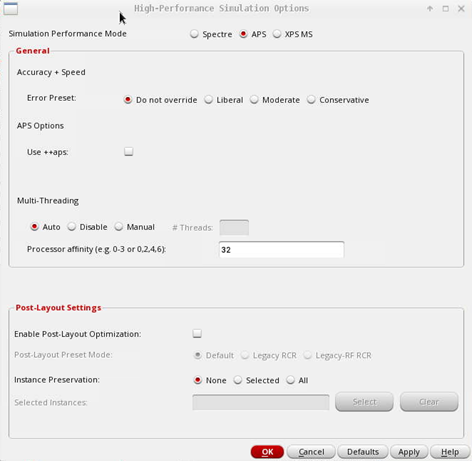

(2)长时间的transient仿真时非常耗时的,我们可以利用计算机的多核处理器,加快仿真速度。在ADE L 窗口中,Setup | High-performance simulation ,然后启用 APS 加速模式。

¶ 3.4 Parametric分析

¶ 3.4.1 基本流程

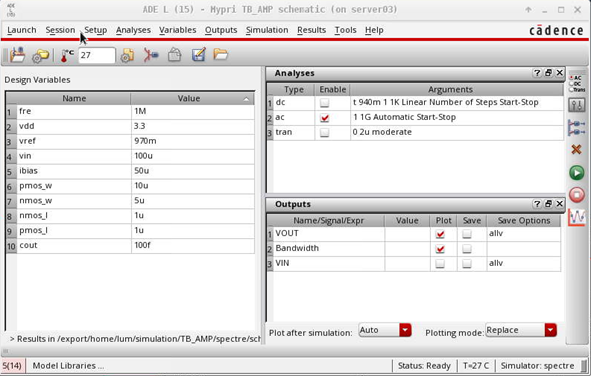

(1)接下来,这里介绍 Parametric analysis 的方法。首先,将ADE L窗口配置为下图所示的样子,仅保留 ac 分析与两个输出。这两个输出分别是wave和value。我们接下来分析变量cout和ibias对bandwidth的影响。

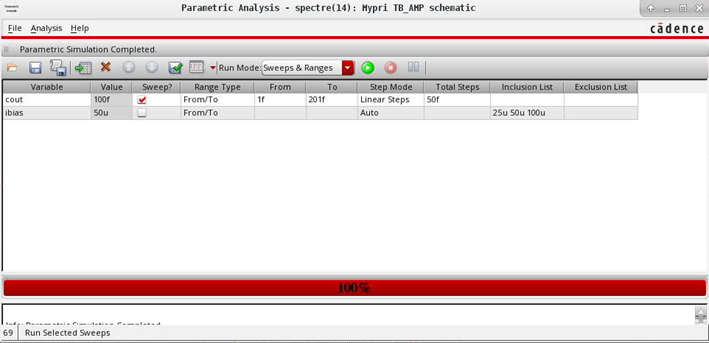

(2)Tools | Parametric Analysis , 然后进行如下配置,

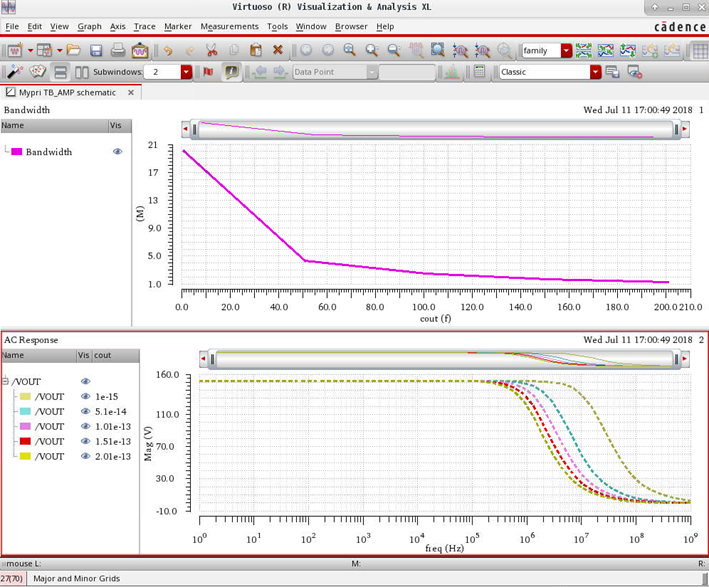

仿真结果为:原来为wave类型的VOUT,在Parametric分析下,生成5条曲线,代表不同cout下的AC响应特性。原来为value类型的Bandwidth,生成了一条曲线,纵坐标是Bandwidth,横坐标是cout,代表Bandwidth随cout的变化。

(3)Tools | Parametric Analysis , 重新进行如下配置,

仿真结果如下图所示,cout有5种选择,ibias有3种选择,原来为wave类型的VOUT,在Parametric分析下,生成可15条曲线。原来为value类型的Bandwidth,生成了5条曲线,纵坐标是Bandwidth,横坐标是ibias,5条曲线分别代表在不同cout下,Bandwidth随ibias的变化。

¶ 3.4.2 Parametric分析的扩展

(1)variable 的顺序不同,Parametric 的输出结果不同。

(2)Range Type, Step Mode…Inclusion List 和 Exclusion List 的配置,可以自由地组合出设计者需要分析的变量组合。

¶ 3.5 其它

(1)在ADE L中,保存state,默认保存选项是 Directory ,那么这里的 Directory 的默认路径为 ~/.artist_state 。同时,我们也可以将其保存在Cellview中,这样,state就如schematic,layout等view在一起了,方便移动。

(2) PSS可以也可以进行类似的transient的仿真,从而可以自由地在时域和频域对结果进行分析,noise是可以对连续电路进行专业噪声仿真工具,在Analysis Choose的列表中,每一项仿真都是为简化分析而设计的,学习方法非常简单。

在CIW窗口,Help | Virtuoso Documentation Library,虽然在线的我们可能无法使用,但是PDF文档绝大多数已经安装在本地了,可以非常便捷地搜索。

(3)相比于IC5,IC6系列,增加了鼠标右键菜单。这是个巨大的进步。

¶ 4. ADE (G)XL仿真

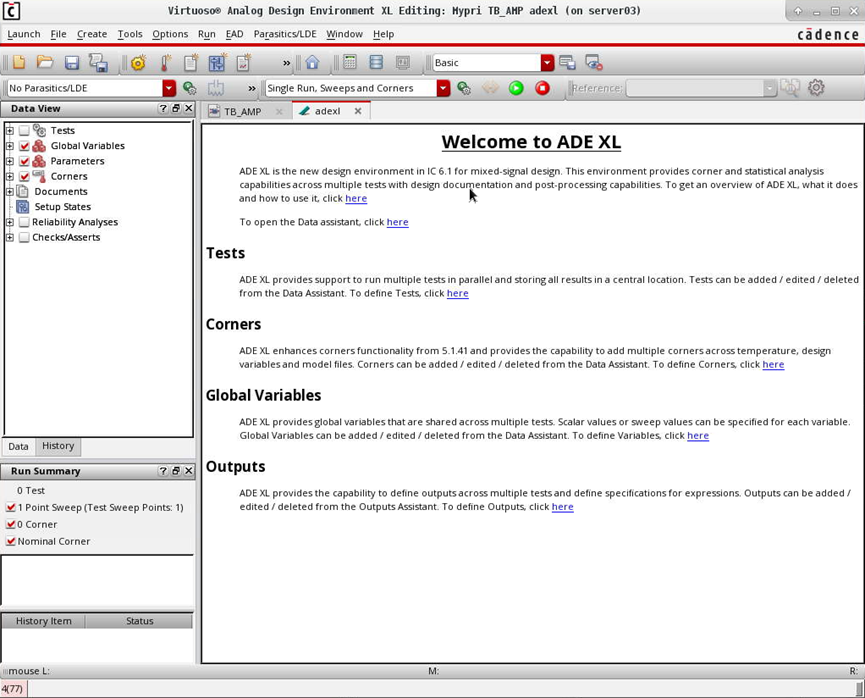

在原理图界面下,Launch | ADE (G)XL | Create New View | OK 即可以启动Analog Design Environment (G)XL。笔者暂时没有发现XL与GXL有什么区别,ADE GXL中的所谓新增的Local/Global Optimization功能在ADE XL中是完全一样的。

点击欢迎页的第一个click here就可以打开官方的《ADE XL User Guide》或《ADE GXL User Guide》,笔者在这里仅做了一些拙劣的简介工作。

¶ 4.1 基本流程

在这一节中,跟随笔者的步骤,你可以快速地从ADE L过渡到ADE (G)XL,并基本体会到其优越之处。

(1)在左上角 Data View 面板中,点击 Test 前面的加号,展开,然后点击 click to add test ,弹出一个ADE L的窗口和 choose Design的窗口。由于我们将ADE (G)XL建立在了Myprj库中的 TB_AMP 的Cell下,所以默认就是选择TB_AMP 的Cell下的Schematic,点击OK。

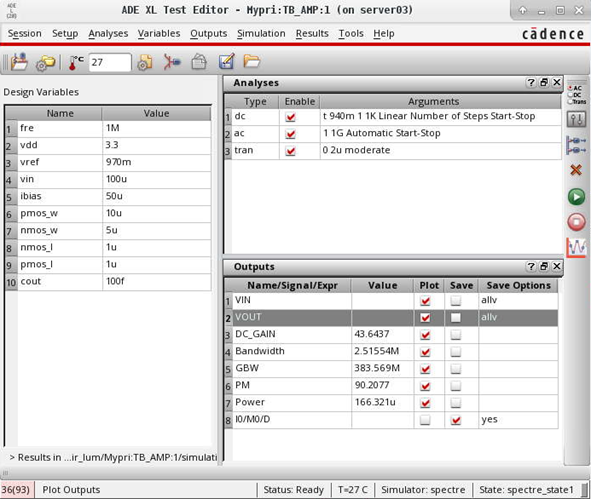

(2)在这个非常像ADE L窗口的ADE (G)XL Test Editor窗口中,我们添加仿真,添加变量,添加输出和ADE L是完全一样的,也可以直接 Load State 。我们通过Calculator,添加相应的指标计算公式。这里 Design Variables,Analysis ,Outputs 列表中项目的顺序可以通过拖动来调整。设置完成之后关闭即可,也可以保存为 state 。

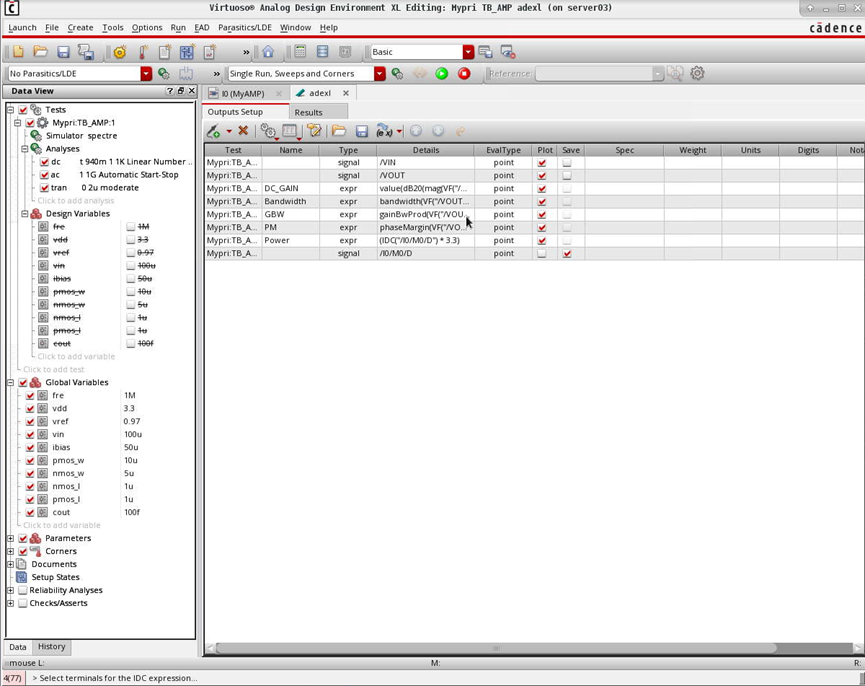

(3)关闭ADE (G)XL Test Editor窗口后,ADE (G)XL的界面发生了变化,我们将加号展开,暂时关闭 Run Summary窗口来更好的截图。Run Summary 等窗口通过 Window | Assistants 重新开启,在第二栏的倒数第3个按钮,是一个下拉菜单,可以选择 Basic, Optimization, Outputs ,读者可以自行尝试。

在中间的标签页 I0(MyAMp) 和 adexl,可以在adexl和schematic之间切换。在它下面的标签页 Outputs Setup 和 Result,同样也是切换不同的面板。

(4)在 Outputs Setup 的面板最上面有一排快捷键,将光标移动在上面即可以看到其功能,另外值得说明的是,IC6系列,增加了鼠标右键菜单,在这里也同样适用。

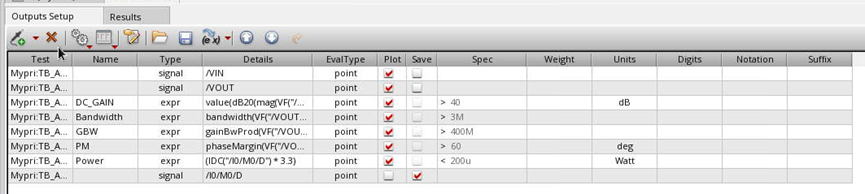

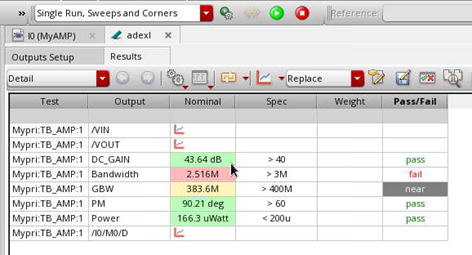

(5)我们在 Outputs Setup 面板中,输入我们想要达到的指标,然后添加相应的单位,数字显示的位数,其余选项是显示格式的设置。总之就是为了更好地显示输出结果。我们简单设置如下:(通过单击或者双击相应的表格)

(6) 点击绿底白三角的仿真按钮,adexl自动切换到 Results 标签页。我们看到,wave 类型的结果成为了图表,双击即可以打开观察,而 Value 类型的结果,则根据距离我们定义的 spec ,有不同的颜色,且有我们刚才增加的单位 Units 。

(7)想要将Bandwidth和GBW达到性能指标,最简单的办法是减小cout(通常cout是由后级电路决定的,作为设计参数或许并不合适,但我们这里这样做仅是为了方便演示ADE (G)XL的使用方法)。

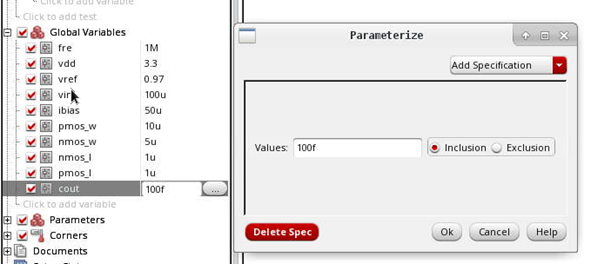

在 Date View 的面板中,在 Global Variables 中,找到cout,左键双击100f, 然后点击右侧出现的按钮,就会出现如下窗口

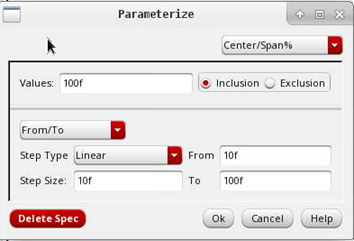

(8)在弹出的窗口,我们点击 Add Specification 右侧的下拉箭头,选择 From/To ,配置如下,点击 OK ,然后运行仿真。

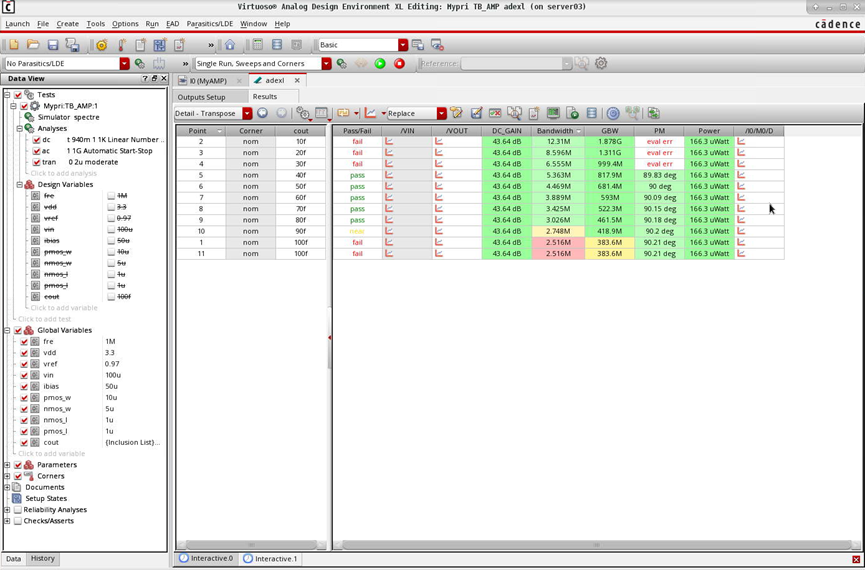

(9)在 Results 面板中,我们观察到了11次仿真结果,在做下面同时出现了Interactive.0 和 Interactive.1 两个标签页,读者尝试点击后发现这其实是本次和上次的仿真结果。

在 Results 面板中,左上角Detail的下拉菜单中,选择 Detail-Transpose ,然后点击表头 Bandwidth 两次,让结果按照 Bandwidth 由大到小排列,我们发现当cout取80f时,即可以满足要求。(忽略eval err,我们稍有常识就可以知道,这个电路的相位裕度是90度,甚至可能都大于这个值,这里我们用了Calculator中的PhaseMargin函数,可能略有不兼容。)

¶ 4.2 优化工具Optimization

我们还可以通过 Optimization 工具来找到设计参数。

我们现在的问题是,GBW指标不符合要求,我们后一级的电路无法改变,即cout无法改变。我们发现功耗指标还有较大空间,因此我们可以通过增大电流,来使得性能达标,但是改变偏置电流ibias,将影响直流工作点vref,因此vref也需要调整。

(1)首先在 Global Variables 中,将cout改为100f,配置ibias区间为50u-70u,步长为2u,配置vref区间为0.92-1.06,步长为5m。

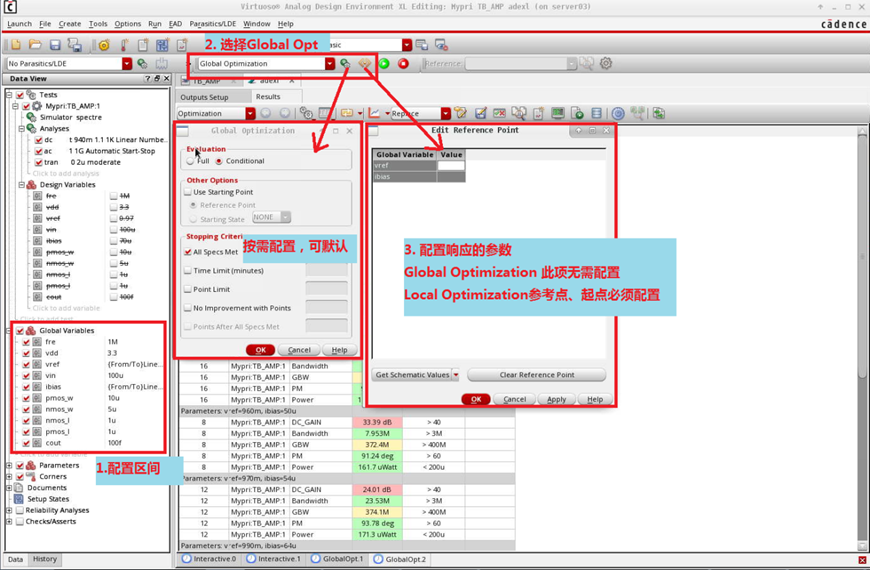

(2)在第三栏中,将 Single Run, Sweeps and Corners 改为 Global Optimization , 右侧的绿色箭头可以配置一些信息,再往左侧的两个黄色箭头,配置参考点,

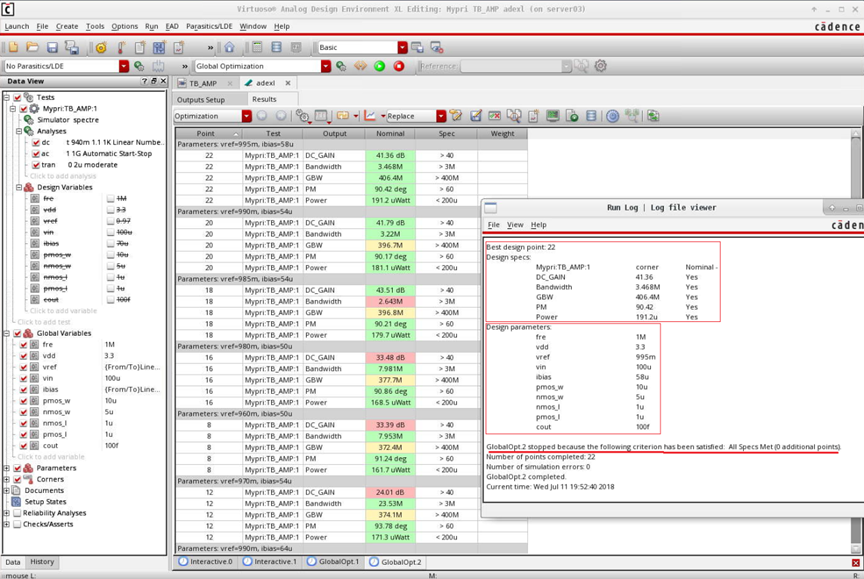

(3)运行结果除了在 Results 中的细节外,还有一份 Run Log 的报告,报告首先给出了当前的性能指标,然后给出了设计参数的数值,最后几行字是在说因为它找到了,所以它停了。

(4)这里需要做简单说明,无论是Local or Global Optimization,仿真器使用的是具有一定优化算法的迭代运算。这里的变量可以是2个,也可以很多。甚至即使参数都符合设计指标时,我们同样可以使用Optimization去进一步优化器件参数。

(5)点击 Window | Assistants | Variables Display ,可以看到当前的变量配置情况,方便Back Annotate。

(6)更多的 Optimization 的使用技巧,请参阅《ADE GXL User Guide》。在 CIW 窗口,点击 Help | Virtuoso Documentation Library 。

¶ 4.3 Corners 仿真

ADE (G)XL的一个巨大进步,是极大程度上优化了Corner的仿真。

¶ 4.3.1 Model文件综述

我们进入到 ../models/spectre/ 目录中,看到很多文件,以tsmc13rf为例。

(1)rf013_v1d3.scs 和 ResModel.scs 是真正的spectre模型文件,这些文件中的数据记录了所有器件模型的参数。

对于每一类型的Mosfet,通常有5种Corner,tt/ff/ss/sf/fs,这里的t代表typical model,f代表fast model,s代表slow model,第一个字母和第二个字母分别表示NMOS和PMOS。

对于除Mosfet之外的器件,例如电阻电容,通常有3种Corner,tt/ff/ss,字母含义相同,但是基本没有P-type和N-type的区别。

需要注意的是,这里的MOSFET模型,一般是BSIM3或者BSIM4的模型,是由University of California研发且目前广为使用的计算机计算模型。相比于我们教科书上的二阶模型,例如n-Mosfet饱和区电流公式

BSIM3/BSIM4的模型更为复杂也更为精确。具体请参阅:《BSIM3v3.3 MOSFET Model Users’ Manual》,《BSIM4v4.8.0 MOSFET Model User’s Manual》。

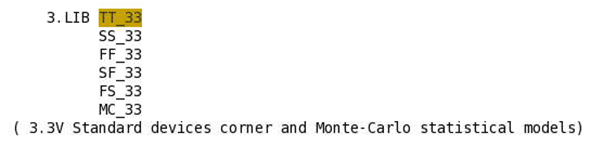

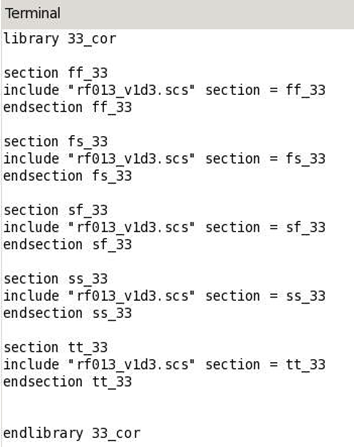

(2)cor_rfmos.scs 等以 cor 开头的文件,这些事将器件分类,每一类器件拥有一个cor_*.scs 的文件,利用 vi 命令打开可以观察到,里面有一句

section = ff_rfmos。这里的 ff_rfmos ,就是调用了 rf013_v1d3.scs 中fast-p/fas- n RF mosfets的模型数据,这类 cor_*.scs 的文件,我们将会在Corner仿真中使用,作进一步介绍。

(3)RF_12_33_FSG.pcf ,是以pcf格式,为我们建立了3个corner文件,但是IC6系列,并不能完全识别pcf文件路径的调用方法,因此不能直接使用。

(4)tsmc13rf.scs 文件,利用vi命令打开可以观察到,里面讲所有器件的tt模型打包成了一个整体。在ADE L窗口,Setup | Model Library 中,我们需要为每个器件定义一个model,意味着我们需要调用 rf013_v1d3.scs 文件n次,然后分别在section中填写 tt_rfmos,tt_mimcap… 这显得很笨拙。我们可以通过这个Model Group的文件,一次性添加所有的器件模型。

(5)这些文件,我们也可以自己编写,只要保证格式正确,可以让工作效率大大提高,具体的格式请参阅IC617自带的PDF帮助文档。

¶ 4.3.2 Corner仿真流程

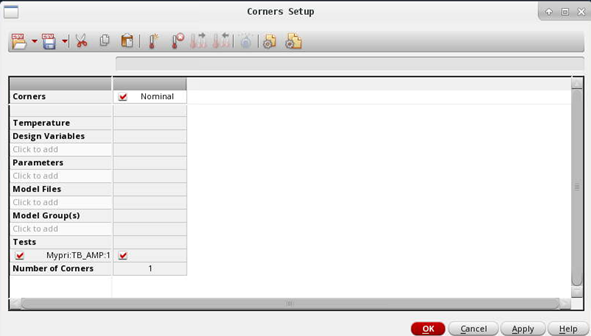

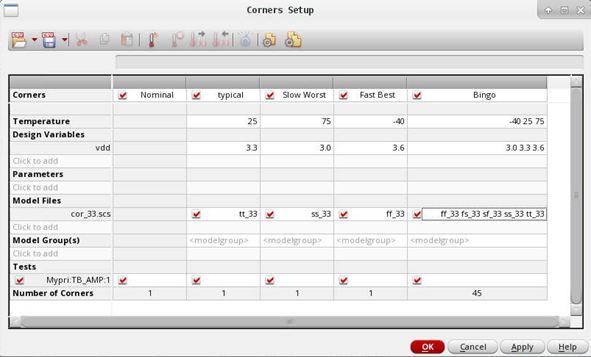

(1)配置Corner,在ADE (G)XL窗口左侧的 Data View 面板,找到 Corners 的分组,展开分组,点击 Click to add corner ,会弹出 Corners Setup 的窗口。

最上面一栏是菜单,光标移动在上面即可以显示功能,请尝试并熟悉界面,在这里也可以使用鼠标右键菜单进行相应操作。

(2)我们返回原理图,其实我们只使用了一种器件,即3V的MOS管,分别是pmos3v和nmos3v,我们观察rf013_v1d3.scs文件,发现,我们应该使用的是baseband库中的以下这些模型:

这些文件,在cor_33.scs的文件中已经定义:

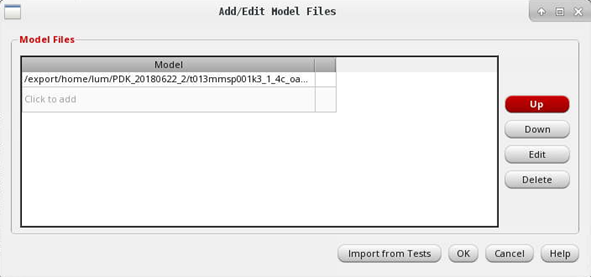

(3)现在,我们可以这样做,在 Corner Setup 的窗口中,在 Model Files 下面点击 Click to add,找到 cor_33.scs 的路径,添加文件,点击 OK 。

(4)在 Corner Setup 窗口,点击菜单栏的中的 add corner 按钮,菜单栏左数第6个,点击4次,增加4个corner。然后通过双击或者单击,Corner表格配置成下图的样子。

这里的Nominal,是ADE L窗口中的Model、参数、温度配置的仿真结果,一般而言,和typical corner的配置是一样的。

Typical,Slow Worst,Fast Best我们逐一配置了3种典型的corner。但是问题是,我们的温度变化有3种,电源电压变化也有3种,MOSFET模型变化有五种,若我们逐一组合,一共有45种组合,难道我们要去逐一配置45列corner么?

答案是可以的,但是逐一配置,若器件类型增加,这几乎是不可能完成的。现在观察Bingo这一列,我们可以把变化的情况写在一起,以空格分开,在Number of Corners的统计数据中,软件已经自动为我们组合好45种corner了。

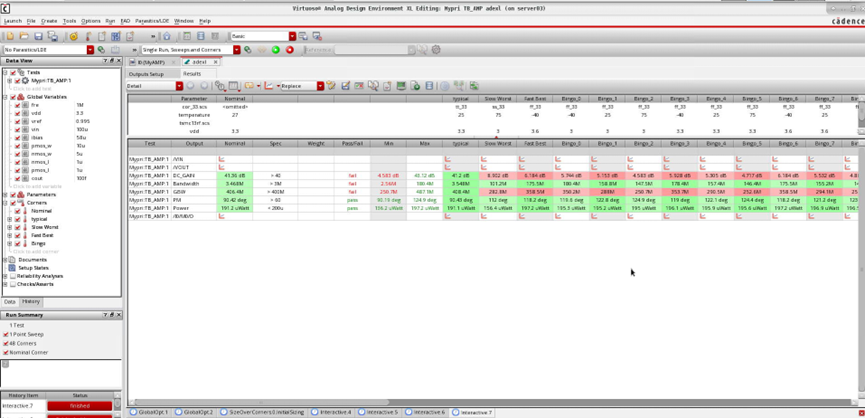

(5)点击确定,关闭Corner Setup窗口,也可以将该配置文件存储成.sdb或者.csc文件,方便其它工程使用。之后在ADE (G)XL窗口运行仿真。注意,仿真运行类型为 Single Run, Sweep and Corners 。

我们观察到仿真器一共运行了48组仿真,每一组信息,以及corner的配置情况都非常清楚地显示出来,我们还可以通过Results面板左上角的下拉菜单选项,把Detail切换成其它形式,方便我们观察分析。

(由于我们的放大器采用了一个非常糟糕的直流偏置策略,电路略有偏差,直流偏置点就歪了,我们主要的目的是介绍软件使用,请原谅并忽略这些细节。)

¶ 4.4 Monte Carlo 仿真

¶ 4.4.1 Mismatch与Process Variation

所谓蒙特卡洛仿真,主要是针对器件的Mismatch,即器件尺寸的失配误差引起的电路性能的变化。Mismatch除了器件尺寸,还可能(取决于工艺厂)包括一些与性能参数相关的工艺参数,温度系数,阈值电压,栅氧电容等工艺参数。

例如,当你设计一个宽度为5um的PMOS,当这个PMOS实际被半导体铸造厂制造1000个出来时,其尺寸真的都是5um吗,事实上不可能。我们统计实际的tape out尺寸,结果服从个以5um为中心,以某一sigma为偏差的高斯正态分布曲线。

我们在蒙特卡洛仿真的设置选项中,还会看到Process的选项,Process更多指的是wafer与wafer之间工艺参数的差异。

总结起来就是,Mismatch的仿真让我们更加关注电路的Matching问题,解决方法通常是增大Width和Lenth的乘积。配合Process的仿真,我们可以在很早设计阶段,估算一下tape out的良率,为提高产量提供参考信息。

另外需要注意的是,虽然在仿真工具中,有Mismatch Only,Process Only,Both的选项,但这个需要工艺厂提供的Model File的支持。

¶ 4.3.2 MC仿真流程

如果我们要仿真Mismatch,只需要将器件替换成后缀带有_mis即可。例如,将mimcap器件替换成mimcap_mis器件。

如果我们要仿真Proecess,我们仔细研读 model/spectre/tsmc13rf.scs和rf013_v1d3.scs 文件发现,若我们要使用器件mos3v器件进行MC仿真,我们需要同样同时引用 rf013_v1d3.scs 中关于mos3v器件的两个section,分别是:

- section=stat_33

- section=mc_33

(1)在ADE (G)XL窗口中,在上角的Data View面板中,展开Test,找到我们的Myprj:TB_AMP:1,双击打开ADE (G)XL Test Editor窗口,就是那个非常像ADE L的窗口。

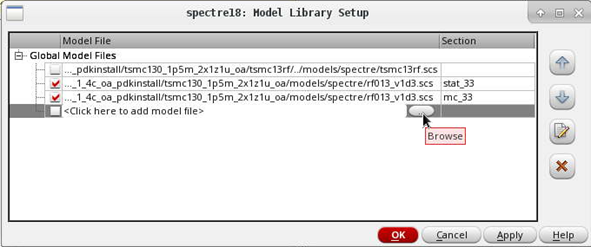

(2)在ADE (G)XL Test Editor窗口,温度设置框旁边的 Model Library 的快捷按钮,双击 <Click here to add model file> ,然后点击右侧 Browse 的按钮,找到 ../model/spectre/rf013_v1d3.scs文件,点击 open,然后在Section栏中填写或选择stat_33,再次添加 ../model/spectre/rf013_v1d3.scs 文件,在Section栏中填写或选择mc_33,去勾选原来的Model文件,最终的样子应该是:

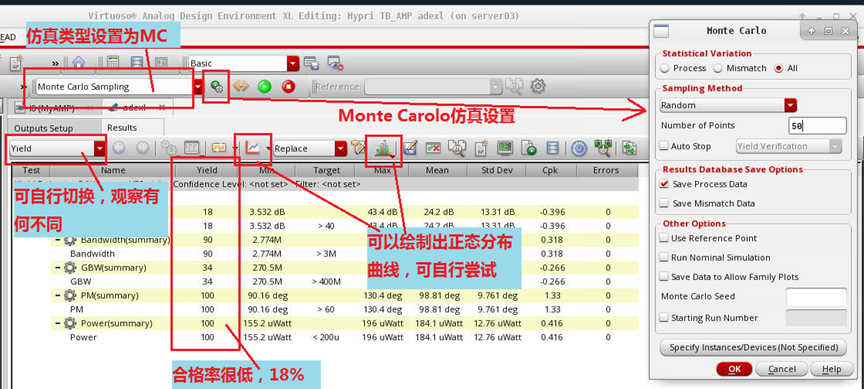

(3)点击 OK,关闭ADE (G)XL Test Editor窗口,返回到ADE (G)XL窗口,将仿真类型从注意,仿真运行类型为 Single Run, Sweep and Corners 切换到 Monte Carlo Sampling 。

(4)点击 Monte Carlo Sampling 下拉菜单右边的绿色设置按钮,打开设置页面。按照需要设置process & Mismatch 还有需要仿真的次数,设置完成后,点击开始仿真按钮。

下图的红体字,大概介绍了MC仿真后如何观察数据的方法。例如绘制分布直方图等方法请自行探索。

(5)更改MC Model文件,除了在 Model Library Setup 窗口中逐一设置,也可以利用打包的方法,将所有信息配置在一个 .scs 文件中。甚至可以额外增加一个名为MC的Corner,将MC的Model文件定义为一个Corner,这样就可以在ADE (G)XL窗口中通过勾选框一键切换了。

¶ 5. 参考文献

- School of Engineering, University of Edinburgh, 2017, “Using Cadence IC6”.

- Cadence Design Systems. Inc., 2017, “Virtuoso Analog Design Environment GXL User Guide”.

- Forum: EDABOARD, Access from: www.edaboard.com.