SDM为了继续提高信噪比的方法:

- 提高OSR导致更大的功耗

- 提高阶数导致稳定稳定性问题和更小的输入范围

- 提高quantiser的step,需要配套的高线性度的DAC,因此很少有超过4~5bit的量化器

这些办法总有限制,另辟蹊径的一条路,就是MASH(Multi-stAge noise SHaping)

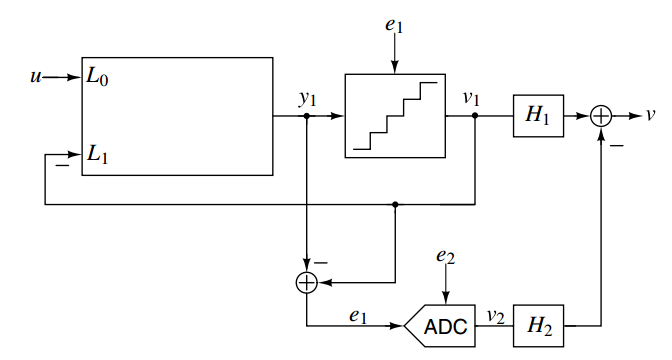

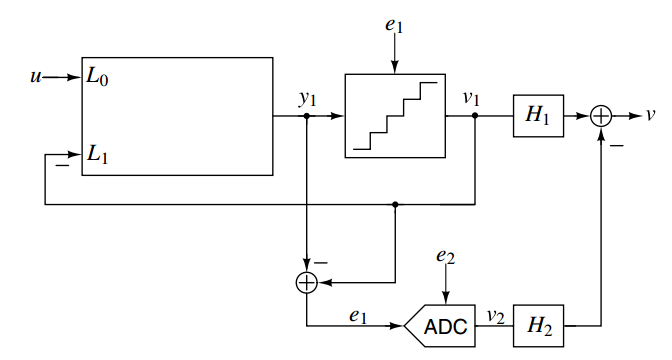

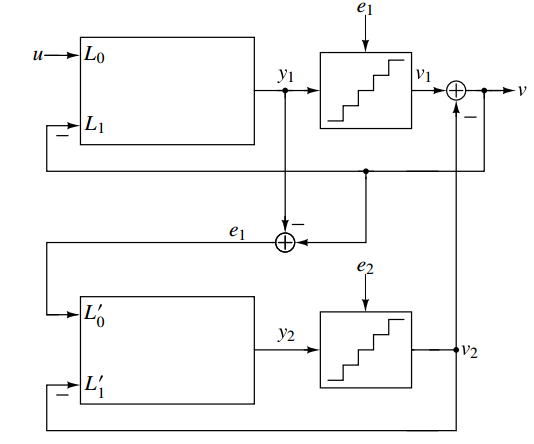

如图,这种结构:

- 将v1−y1相减的结果,其实就是e1;

- e1注入到下面的ADC中,v2包含输入信号e1以及新增噪声的e2

- 将两个结果各自经过一个数字滤波器后再合在一起,通常H1=z−k,也就是下面ADC的延迟;H2=NTF1,这样两者合并的时候,e1就会被减掉,只剩下了e2

- e2设计得是比e1更小的一个误差,同时下面的ADC不在上面的SDM环路中,不在乎延迟时间(通过H1就可以把这个延迟时间补偿掉),因此可以用低复杂度的pipeline实现。

传递函数为:

V(z) =[STF1(z)U(z)+NTF1(z)E1(z)]H1(z) − z− k[E1(z)+E2(z)]H2(z)=z−k[STF1U(z)−NTF1(z)E2(z)]

由于e1不能无延迟的减出来,因此第二级的输入改为y1,这样第二级的输入为

Y1(z) = V1(z) − E1(z) = STF1(z)U(z) + (NTF1(z)−1)E1(z)

模拟上的简化的后果,由数字去承担,将第二级的数字滤波器重新做为

H2(z)=NTF1(z)−1NTF1(z)

这种,最终的输出结果

V(z)=z−kU(z)NTF1(z)−1−STF1(z)−z−kE2(z)NTF1(z)−1NTF1(z)=z−kU(z)1−NTF1(z)STF1(z)+z−kE2(z)1−NTF1(z)NTF1(z)

在输入信号的带看范围内,NTF1(z)≪1,最后结果应该非常接近于无延迟滤波的结果。这个结构的缺点是第二级的输入包含输入信号u和噪声,输入信号很大,且第二级ADC应该设计的非常高线性从而避免产生由于大摆幅输入信号导致的谐波失真。

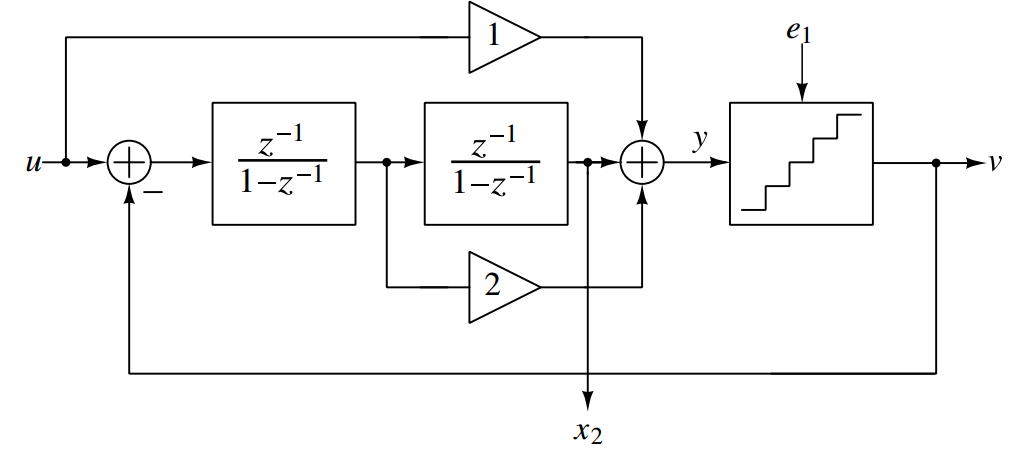

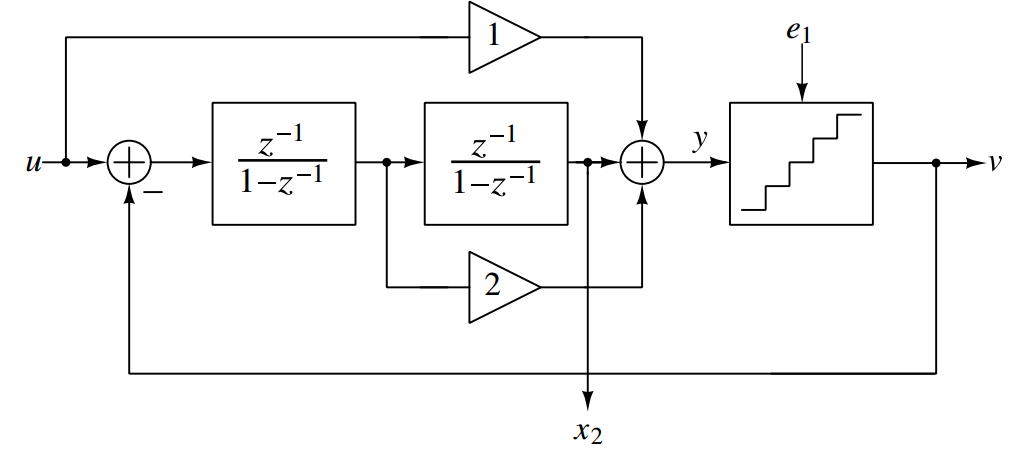

SDM可以选择CIFB with input forward结构的,但是最后一级积分器的输出是(1-NTF)E,这个噪声的信号方差要高于E,最佳的选择,还是CIFF,因为它最后一级积分器的输出信号就只包含E,如下图所示

X2(z)=z−2E(z)

具体的sensitivity见下面的分析,这里单独分析summer部分做出的这个“相减”动作,如果不准确,是否会有影响:

这里的从输入到SUM的前馈1系数是否准确,确实会影响x2是是否包含输入信号u,但是泄露到MASH2的u,本质还是输入信号,这部分信号(是一个低频信号)与MASH1相加的时候,还会乘以NTF1这样一个高通滤波函数,因此会被抑制。没有被抑制的部分,可能也是表现为一个微弱的增益误差?

而进入到x2的e1部分到底是多少,还是由NTF1来决定的,NTF1是噪声环路的系数,基本上与STF1信号环路的系数关系不大;

总之,summer这里的快速前馈1,对于MASH的最终是否能够很好的抵消的影响不大。

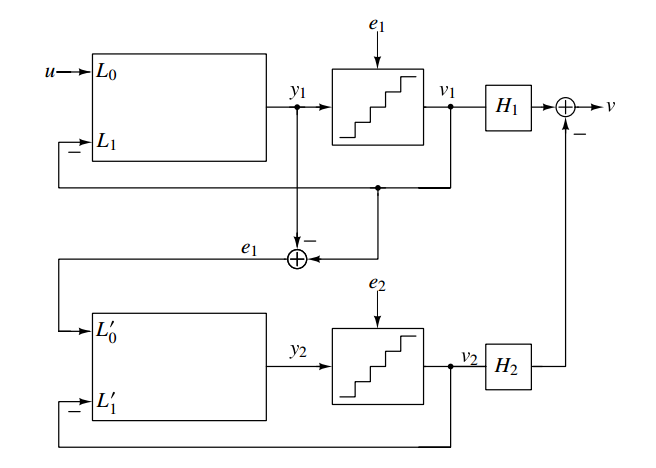

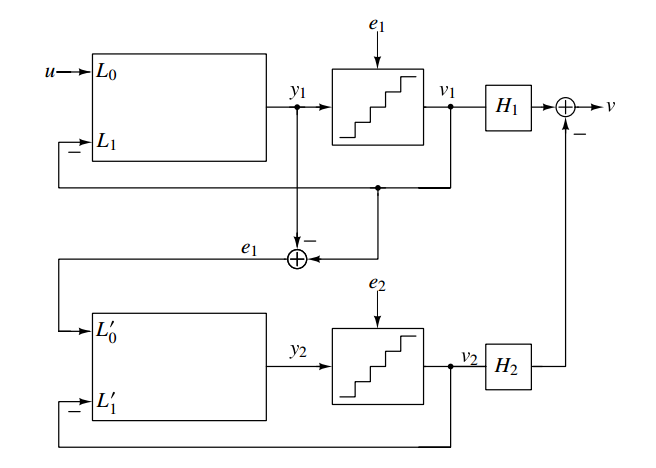

上图的结构,各自的传递函数为

V1(z) = STF1(z)U(z)+ NTF1(z)E1(z)V2(z) = STF2(z)E1(z)+ NTF2(z)E2(z)

设计数字滤波器,目的是去抵消掉E1,在上面的例子中,可以有如下形式:

H1H2=STF2=NTF1

最终的表达式为:

V(z)=STF1(z)STF2(z)U(z)+NTF1(z)NTF2(z)E(z)

得到这样表达式的前提是

NTF1(z)STF2(z)−STF2(z)NTF1(z)=0

同理,这种结构需要用到free delay的v1(z) − y1(z)是需要用Low-Distortion结构的SDM的结构。比如Silver-Steensgaard,使用Low-distortion结构还有其他好处:

- 第二级的输入是噪声,可以让e2表现得更像白噪声;即使第一级给出的输出信号V1里仍存存在tones,最终的输出V中的idle-tone也会被抑制,因此MASH通常不需要dither(因为idle-tone就是量化器产生的周期性的量化噪声,由于MASH-MOD2的输入信号里包含这个idle-tone,同时MASH-MOD2的输入信号很接近白噪声而不是一个有理分数,所以v2本身不含idle-tone,且把输入信号的idle-tone很好的量化出来了)。

- 第二级可以大胆地去使用多BIT DAC而不用担心其Mismatch导致的非线性,因为DAC引入的非线性误差会乘以H2(z) = NTF1(z)之后再汇入v(z),NTF(1)就是一个噪声整形。这样MASH-MOD2的DAC有了像MASH-MOD1中的quantizer一样的NTF加持。

- 第二级的输入由于不含输入信号,因此不用担心distortion导致harmonics的问题?个人理解是输入信号是无规律的,输入信号没有一个fundmental frequency,自然就没有2nd, 3rd harmonics了。

在单stage SDM中,积分器的有限增益没有太大关系,因为只有L1(V→Y)的增益足够高,这些误差都可以被抑制。但是在MASH中不是这样,噪声是靠下面的减法实现的,需要完全匹配才可以。

Hl1(z)=H1(z)NTF1(z)−H2(z)STF2(z)Hl2(z)=H2(z)NTF2(z)−H3(z)STF3(z)

分析如下:

-

e2不重要,首先e2通常比e1要小;其次Hl2的noise-shaping是双倍阶数的?

-

分析Hl1,NTF1的失配比较关键,STF2的失配相对没那么关键,因为后者可以被数字域的H2=NTF1经行整形,尤其是OSR比较高的情况下。

-

如果我们假设H1=STF2=1,则有

∣Hl1∣=∣NTF1a−NTF1i∣

这里下角标a表示actual,i表示ideal

-

继续简化,当∣L1∣≫1时,NTF1=1/(1+L1)≈1/L1,可以得到更简单的leakage传递函数:

∣Hl1∣≈∣∣∣∣∣L1a1−L1i1∣∣∣∣∣

积分器的有限增益传递函数 CH2-MOD1#4.1 传递函数为:

Ia=1−pz−1pz−1,p=A+1A

但是这里,在SDM书中的(5.20)的公式,给出了另一个表达式,这里把他统一

Ia=1−A+1+aA+1z−1A+1+aAaz−1,a=CfCi

书中近似关系的逻辑是

A+1+aA+1≈A+aA≈AA−a=1−AaA+1+aA≈AA−(1+a)=1−Aa+1

接着假设积分器增益a还有D比例的失配,则最终给出的表达式

Ia=1−p′z−1a′z−1 a′=(1−D−Aa+1)a, p′=1−Aa

最终带入简化的∣Hl1∣中去,得到:

∣Hl1∣≈∣∣∣∣∣L1a1−L1i1∣∣∣∣∣=∣∣∣∣∣A1+(z−1)⋅[aD+A1+(1/a)]∣∣∣∣∣

分析这个结果,

- 第一项1/A没有经过(z-1)的整形,因此在低频下增益显得额外重要;

- 但是如果OSR比较低,有越来越到的高频的误差没有被滤波掉,后面的失配以及第一级积分器的增益就显得外重要了

- 同时error in the path coupling errror of fisrt stage and second stage (个人认为这个是v-y的那个过程)的误差也会加进到∣Hl1∣中去,但是这个误差会经过H2的噪声整形;

推导一个二阶的MASH会比较复杂,假设积分器的有限增益误差还是还是和MOD1一样,通过泰勒级数展开,分析在z=1处的(z-1) 的N阶系数

Hl1A0A1A3=A0+A1(1−z−1)+A2(1−z−1)2+⋯=A21=(a11+a21)A1=a1a21−1+2(1−a1a21+a221)A+a1a22D

基本结论是,A1~A3的影响比A0大,因为1/A^2实在是太小了。高次项又受HPF滤波器的影响比较大,因此OSR的影响非常大。

Understanding SDM 2nd Edition, page 126

As an illustration, for A 1000 and D=0.5%, we find that A0=10^-6 and the values of coefficients A1-A4 are between 0.001 and 0.2. The multipliers (1-z-1)L introduce highpass filtering into the terms in H1, which reduces their effects on the inband noise. The reduction increases rapidly with increasing L and OSR. For example, with OSR=64, the linear term (L=1) is reduced by a factor around 1/30, the quadratic term by about 1/1000, and the cubic one by about 1/30,000. Hence only the first three terms are significant.

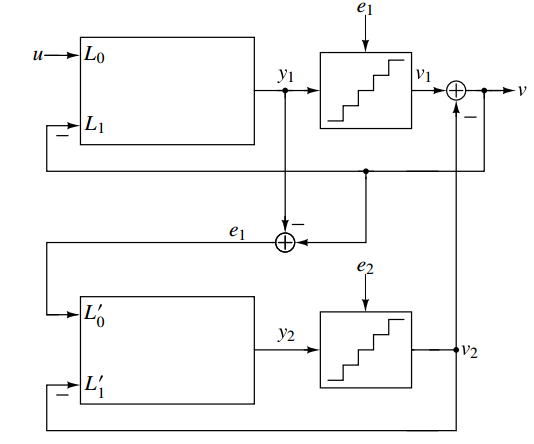

MASH主要的问题是理想的数字NTF与实际模拟电路的NTF如果不匹配,就会有误差,那么如果按照下图的结构实现,sturdy-mash,

V=STF1⋅U−NTF1⋅NTF2⋅E2+NTF1⋅(1−STF2)⋅E1

这个结构,SMASH与MASH的区别是:

- 不存在数字补偿滤波器了;

- 注入到第二级的E1不是单纯的E1,而是NTF1整形过的E1

令(1−STF2)=0看似很简单,但是实际上STF2不可能是一个delay-free的传递函数,因此不可能真正消除掉。另外一种做法是,令STF2=1−NTF1,这样最终的结果是:

V=STF1⋅U−NTF1⋅NTF2⋅(E2+E1)

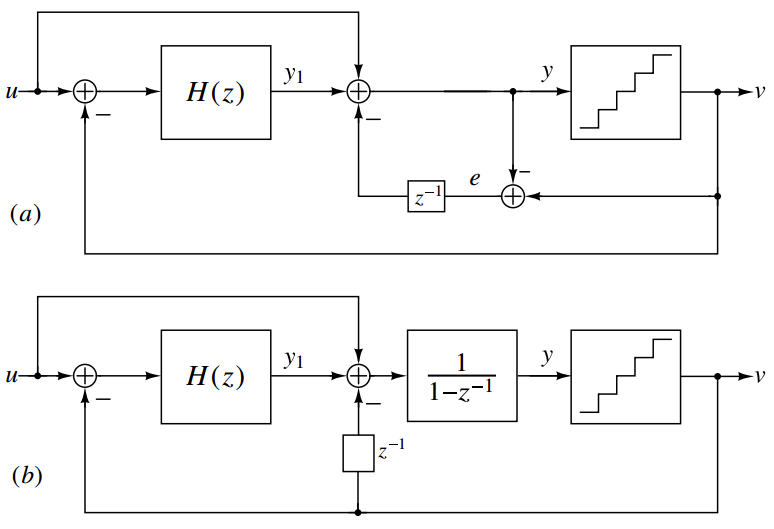

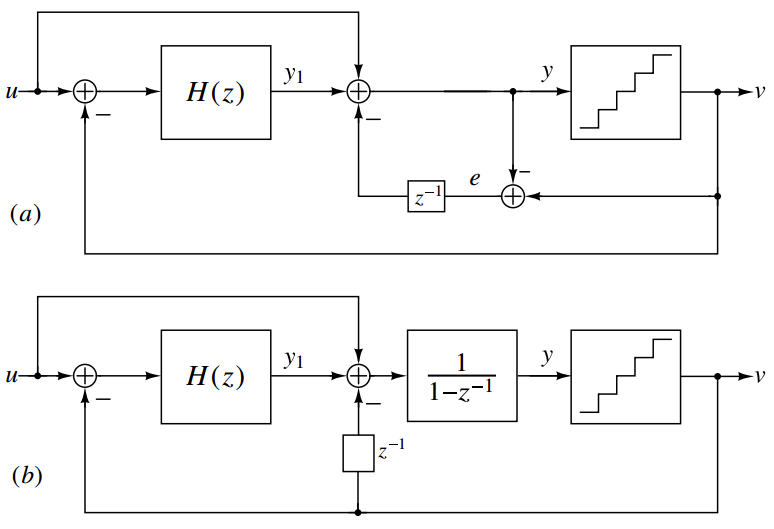

基本特点是,将quantizer的输出输入做差,延迟之后再送入量化器中,(b)是(a)的等价电路理解这个等效电路,其实就是一个线性电路的叠加定理的综合应用

- 图(a)屏蔽掉u,v,只观察y(input)→y(output)的传递,相当于当前的y加上经过延迟的y乘以(-1)*(-1),也就是yo(n)=yi(n)+yo(n-1),这正是一个non-delaying integtrator;

- 图(a),观察y1与y之间的那个节点,除了有yin的输入,其实还有v的输入,v的输入其实经过延迟乘以(-1)

分析该结构的优点

- 使用b结构时,不再需要快速前馈的summer,因此可以省下来一个OTA;

- 输入y端,输入信号的支路增加了,但是实际上幅值并没有增加多少,包含的e[n]-e[n-1]的量化噪声,是weekly correlated(其实完全可以大胆的认为就是非相关的,如果信号能够完全地在一个周期内建立?)因此quantiser的输入范围最多减少3dB

- 这种高通的的量化器输入处的噪声,表现为dither,因此有着很好的SFDR和THD性能,SFDR可以轻松上100dB。

- 由于noise-coupling-network在第一级积分器之后,因此noise-coupling network的mismatch/offset/dc-gain的影响不是很大。