严格地求积分器的传递函数,应该完成一次完整的采样周期:当前采样末(n) -> 积分末(n+0.5) -> 采样末(n+1)

过程一,虚地点的电荷保持不变;过程二,积分器输出维持不变;这样可以列出方程

(0−Vin[n])Cin+(0−Vout[n])CintVout[n+0.5]=(0−0)Cin+(0−Vout[n+0.5])Cint=Vout[n+1]

两个方程,两个未知数Vout[n+1]和Vout[n+0.5],得到

Vin[n]Cin=(Vout[n+1]−Vout[n])Cout

对上述方程进行Z变换,得到

VinVout=CintCin1−z−1z−1

对这个积分器推导时,通常不会引入0.5的概念,因为[n+0.5]和[n+1]积分器的输出维持不变,所以忽略0.5后不会出错。

这种积分器,采样接+Vin,积分时刻输入接−Vin,同理可以列出方程

(0−Vin[n])Cin+(0−Vout[n])CintVout[n+0.5]=(0+Vin[n+0.5])Cin+(0−Vout[n+0.5])Cint=Vout[n+1]

这样,得到

VinVout=1−z−11+z−0.5

分析这个传递过程,输出的变化间隔是Ts=1,而采样输入的间隔是Ts/2=0.5,在很多论文推导采样积分过程时,是会引入n=0.5的概念的。

但是 "Understanding Sigma-Delta Modulator, page 210" 的推导没有考虑0.5这个问题,得出的double sampling积分器的传递函数是

VinVout=1−z−11+z−1

我认为,这样是不准确的,如果输入信号频率比较低时,Vin[n+0.5]和Vin[n+1]可能几乎相等(DC时完全相等),double sampling可以让信号传递×2(KT/C不变,从而提高信噪比),但是OSR较低输入信号频率比较高时,显然Vin[n+0.5]和Vin[n+1]是不等价的。

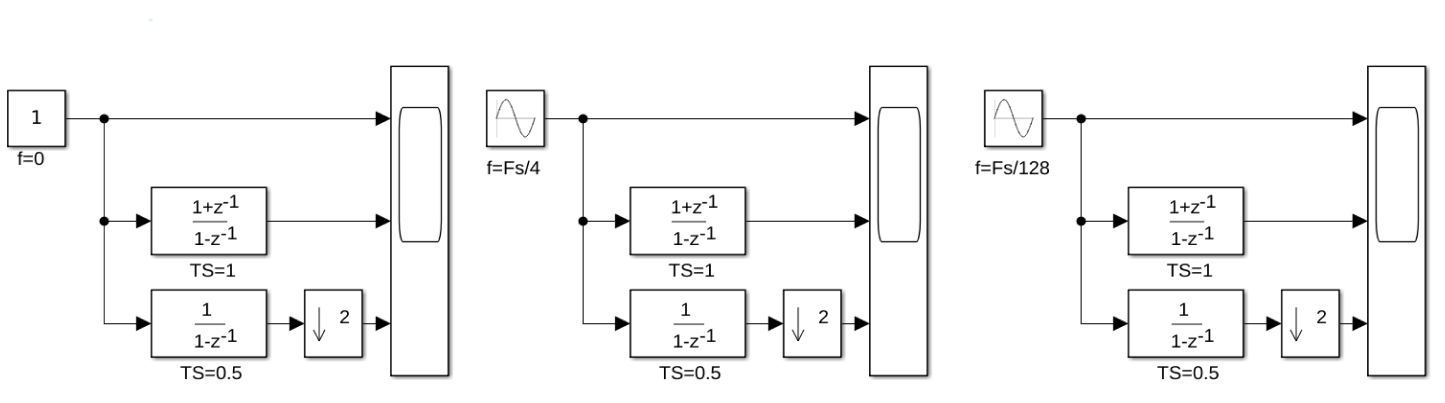

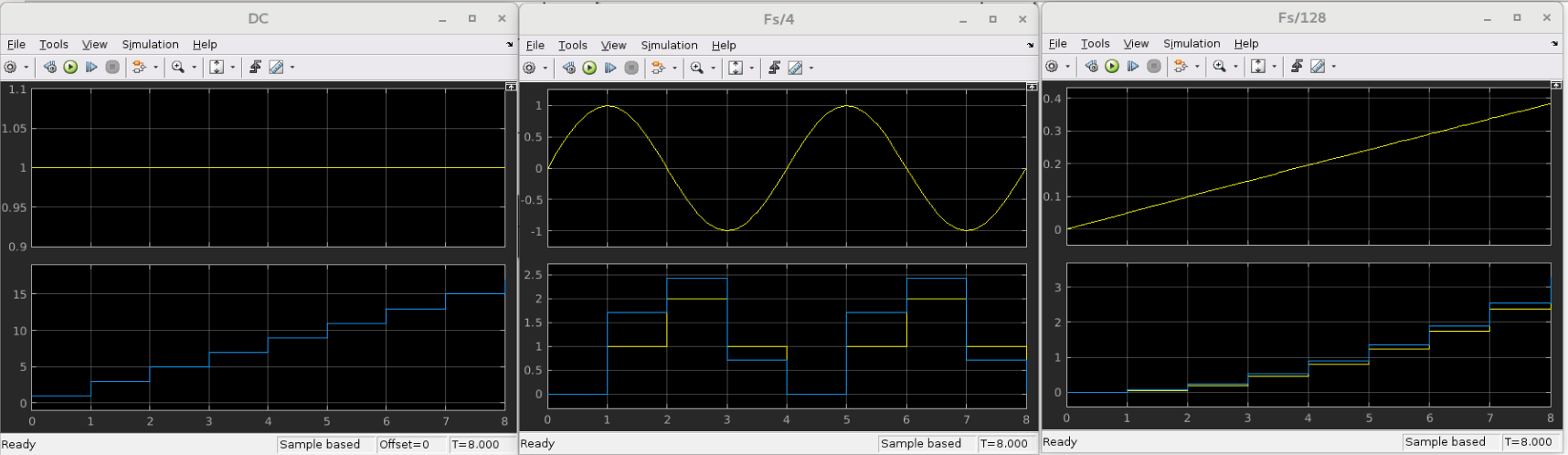

对于电路而言,等效于积分器的积分速率0.5Ts,再经过一个Ts的采样保持系统。对于离散的建模而言,等效于积分器的积分速率0.5Ts,再降采样到Ts;

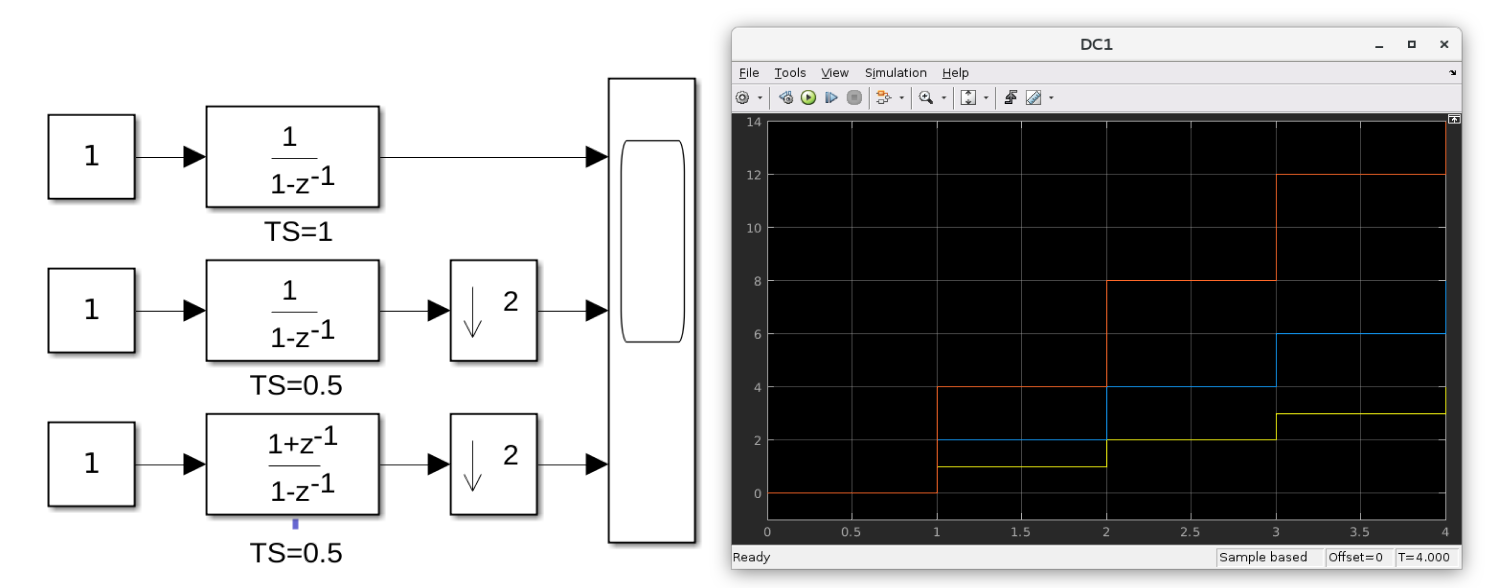

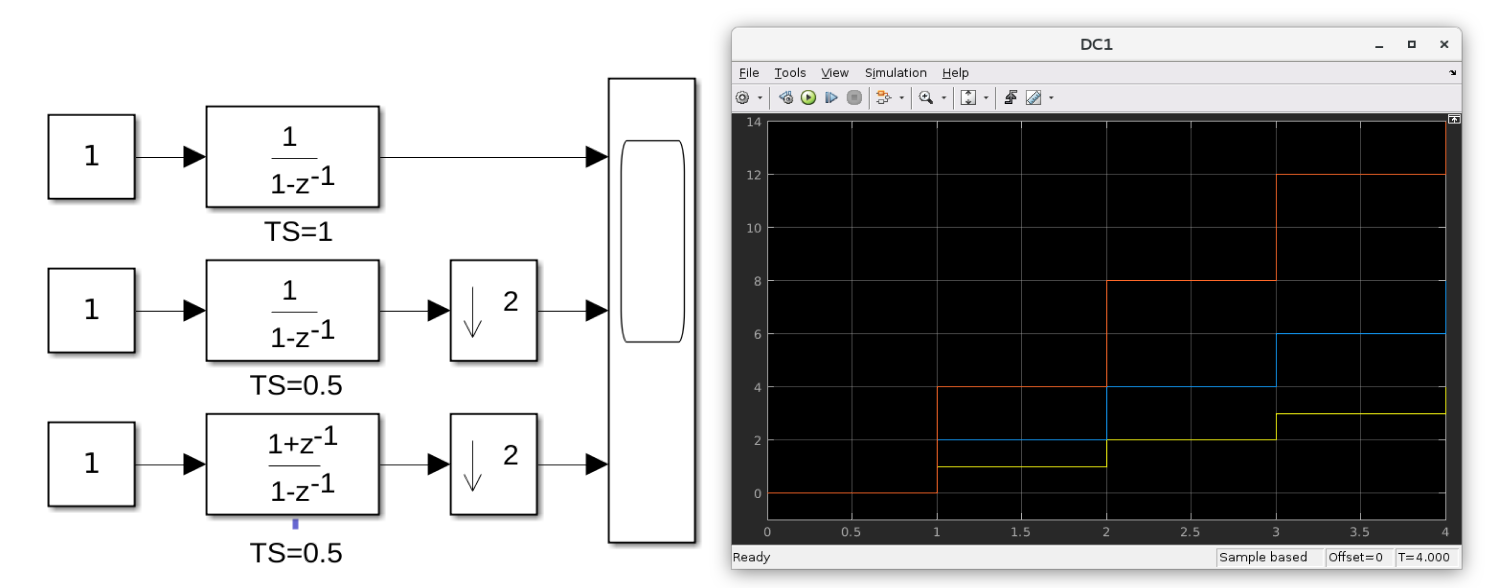

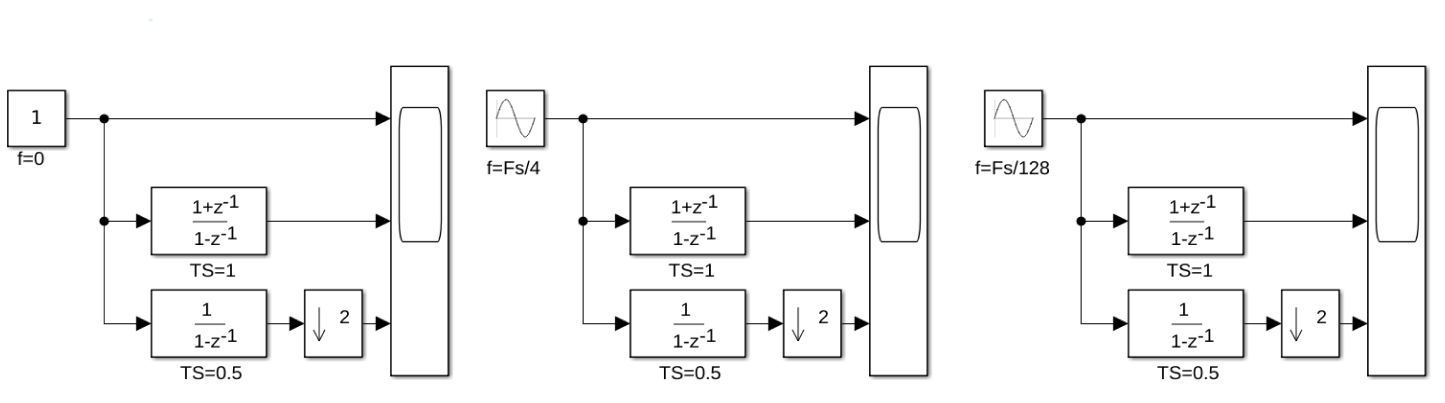

仿真建模如下,信号源是连续的,上下两个积分器的采样速率分别是1和0.5

得到仿真结果印证了上述分析,DC信号完全一样,输入信号频率越高,差别越大。

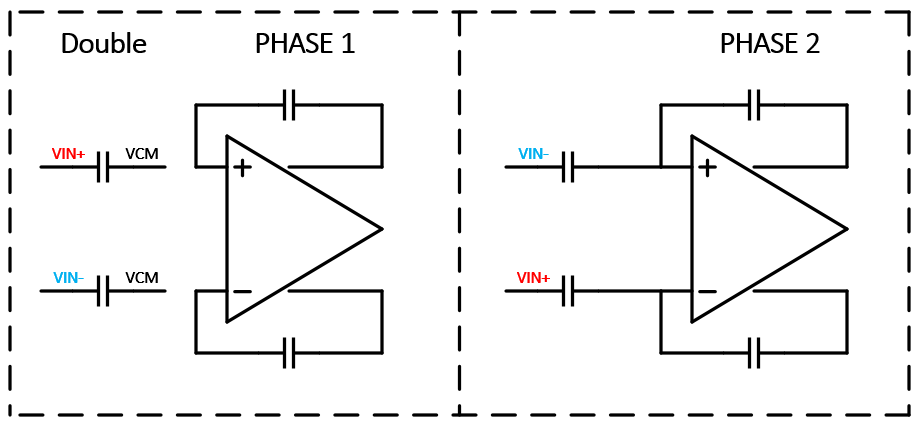

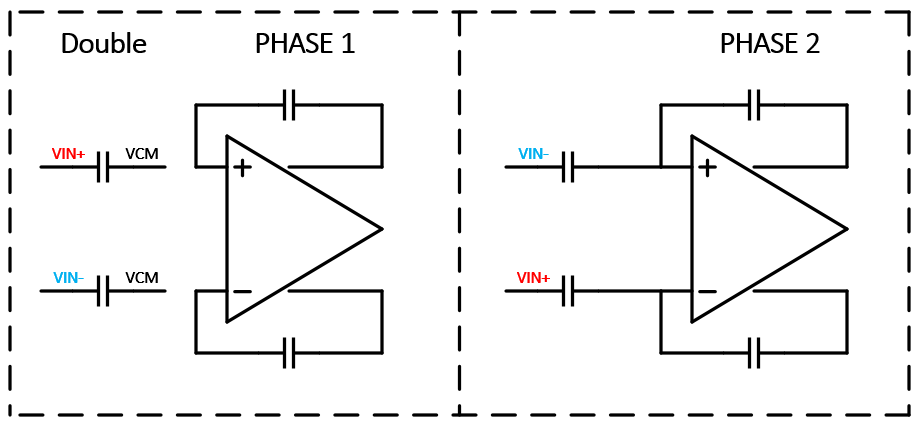

如果是Twin Double Sampling的积分器呢?

- Double:采样接+Vin,积分时刻输入接−Vin;

- Twin:有2个switch-capacitor的采样网络,A采样时B在积分;B采样时A在积分;

列出差分方程

(0−Vin[n])CinA+(0−Vout[n])Cint(0−Vin[n+0.5])CinB+(0−Vout[n])CintCinA=CinB=(0+Vin[n+0.5])CinA+(0−Vout[n+0.5])Cint=(0+Vin[n+1])CinB+(0−Vout[n+1])Cint=Cin

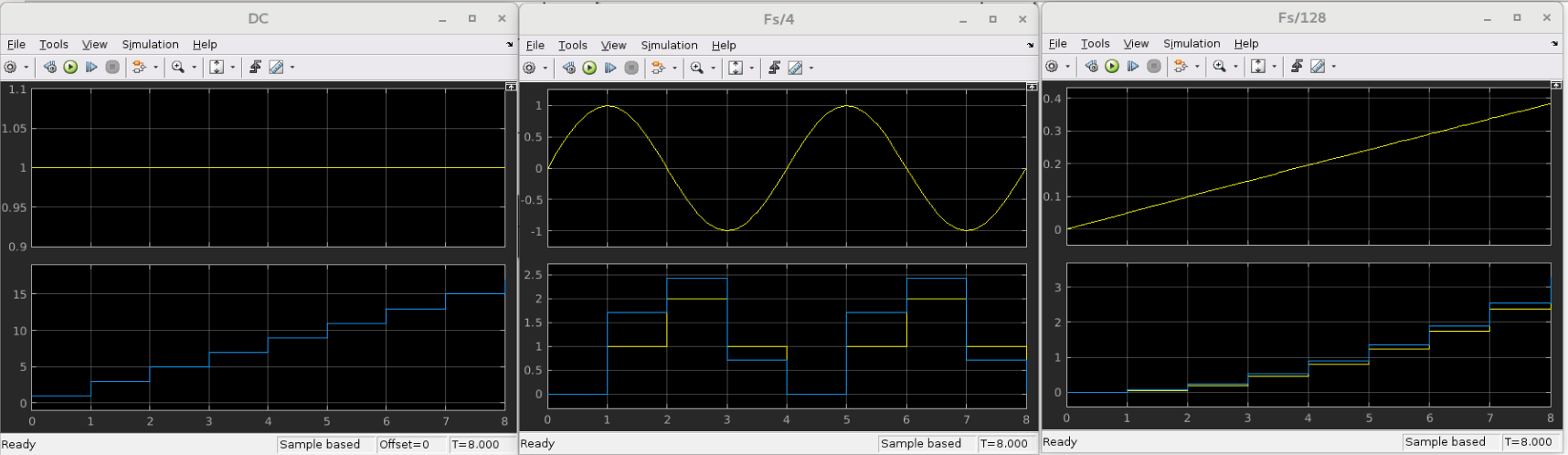

这里的问题,在于第二级积分器的采样速率,如果第二级积分器的仍是double sampling,那传递函数为

TF=1−z−11+z−1z=ejωTsTs=0.5

如果后级是Ts=1的积分器,或者是量化器,则完整的传递函数为

TF=1−z−11+2z−0.5+z−1z=ejωTsTs=1

该系统对于DC或者低频信号,Twin Double 等效于4 x Delayed,2 x Double