¶ 参考资料

高性能电路 Tutorial 合集:Analog Circuit Design, High-speed Clock and Data Recovery, High-performance Amplifiers, Power Management

CDR-OPA-POWERMANAGEMENT.pdf

¶ Structure

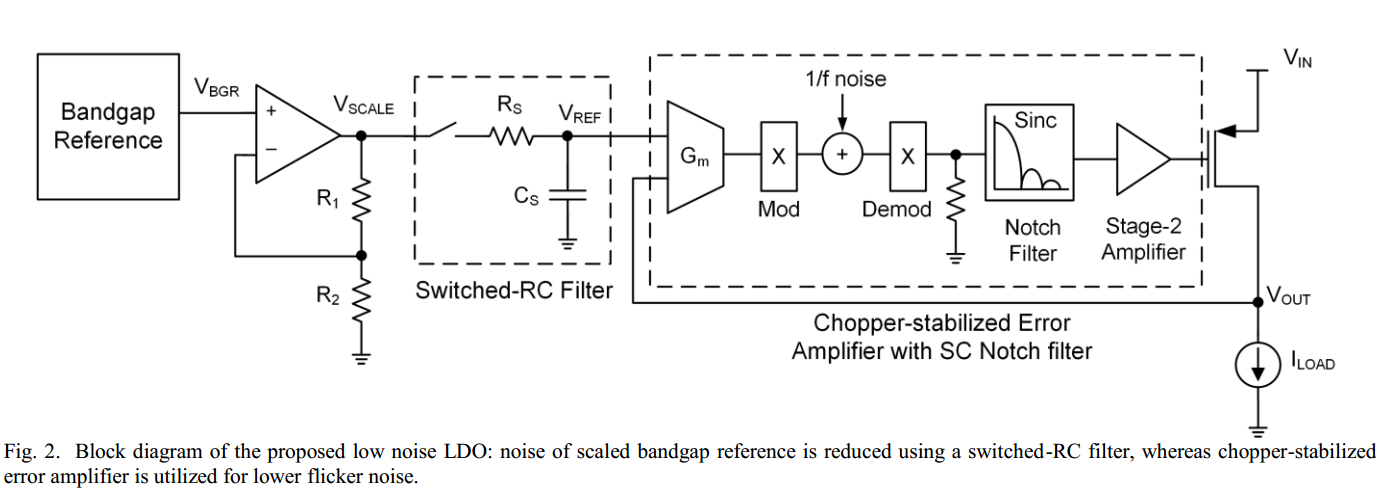

LOW Noise LDO,逐一解决了噪声的三个来源,Bandgap Core, Error Amplifier, Feedback Resistive Divider,主要技术指标如下:

- Process: 0.25um

- Max Load Current: 100mA

- Load Capacitance: Cap-Less

- Integrated Noise 10Hz ~ 100KHz: 14.8uVRMS

- Noise PSD @100KHz: 0.13uV/sqrt(Hz)

- Iq: 40uA

- PSR @1KHz: 50dB

- Area: 0.21mm^2

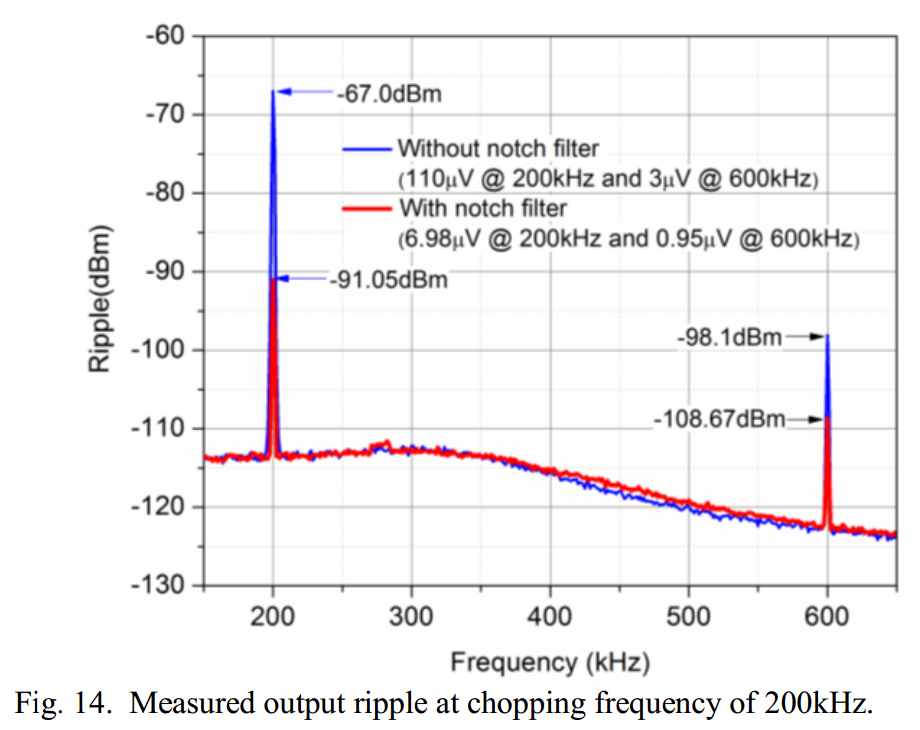

问题是,在 RF/PLL/ADC系统中:7uV 200KHz 的 Ripple 能否接受呢?如何理解这个指标?

¶ Resistive Divider

将 VSCALE 电压放到前面,而不是在输出做;这样电阻的噪声,就可以被 LPF 滤掉了;后面的输出 Buffer 是 Unit-Gain-Configuration,这样也更更容易做;

¶ Bandgap: S/H RC-Filter

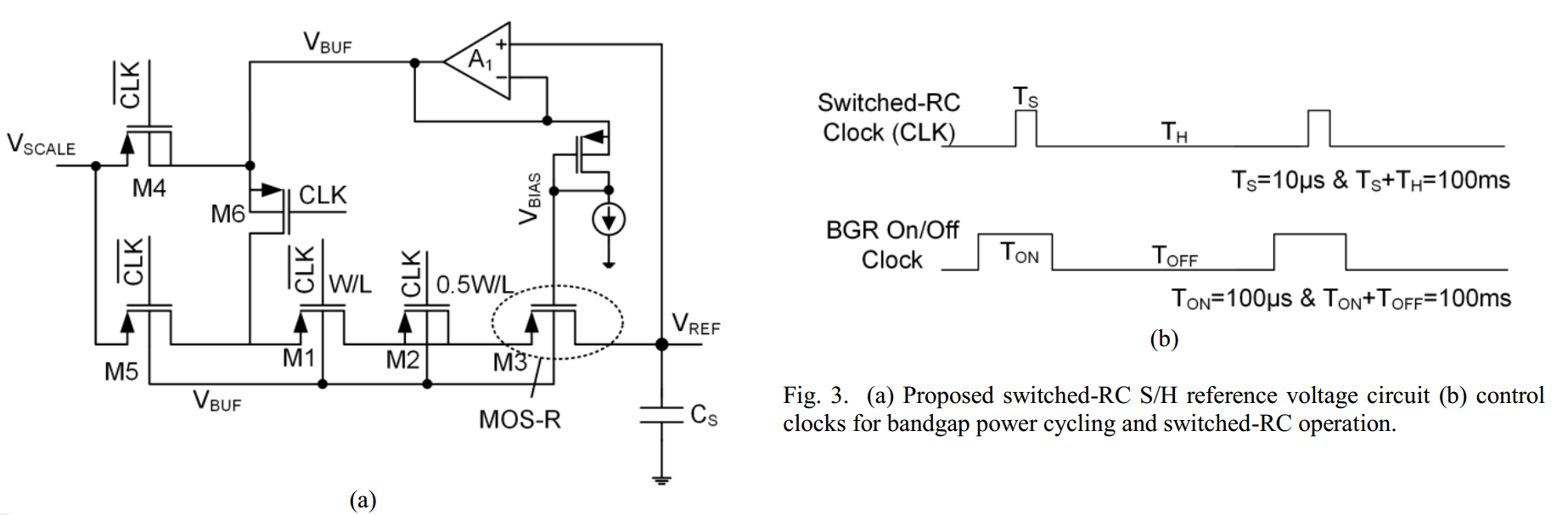

Bandgap Core 的噪声主要通过低带宽去解决,片上集成一个 1Hz 的 LPF 是很困难的(通常需要片外电容)。这篇文章是通过 S/H 电路,用一个 Duty Cycle 仅有 0.01% 的 Pulse 去间歇性地导通 Bandgap 电压,其余时刻就用电容上的电压。

在这样的欠 Settle 下,甚至连 KT/C 噪声都会乘以 Duty-Cycle D 被衰减掉?论文给出的计算公式是不合理的,Murman 教授在计算会回归到噪声的本质 -- 时域相关 -- 去进行计算,这部分有待进一步计算论证。

开关的漏电用 A1 这个运放钳位,保证 Vds/Vdb 几乎没有压差,残差是 A1 的 Vos;开关的 Charge Injection 用 Dummy MOS 解决,这篇论文也提出了 Channel Charge 更倾向流入低阻的一边。

LPF 的启动时时 Bypass 的,不然启动在 1Hz 的LPF下就太慢了。

¶ Chop-Stabilized Error Amplifier

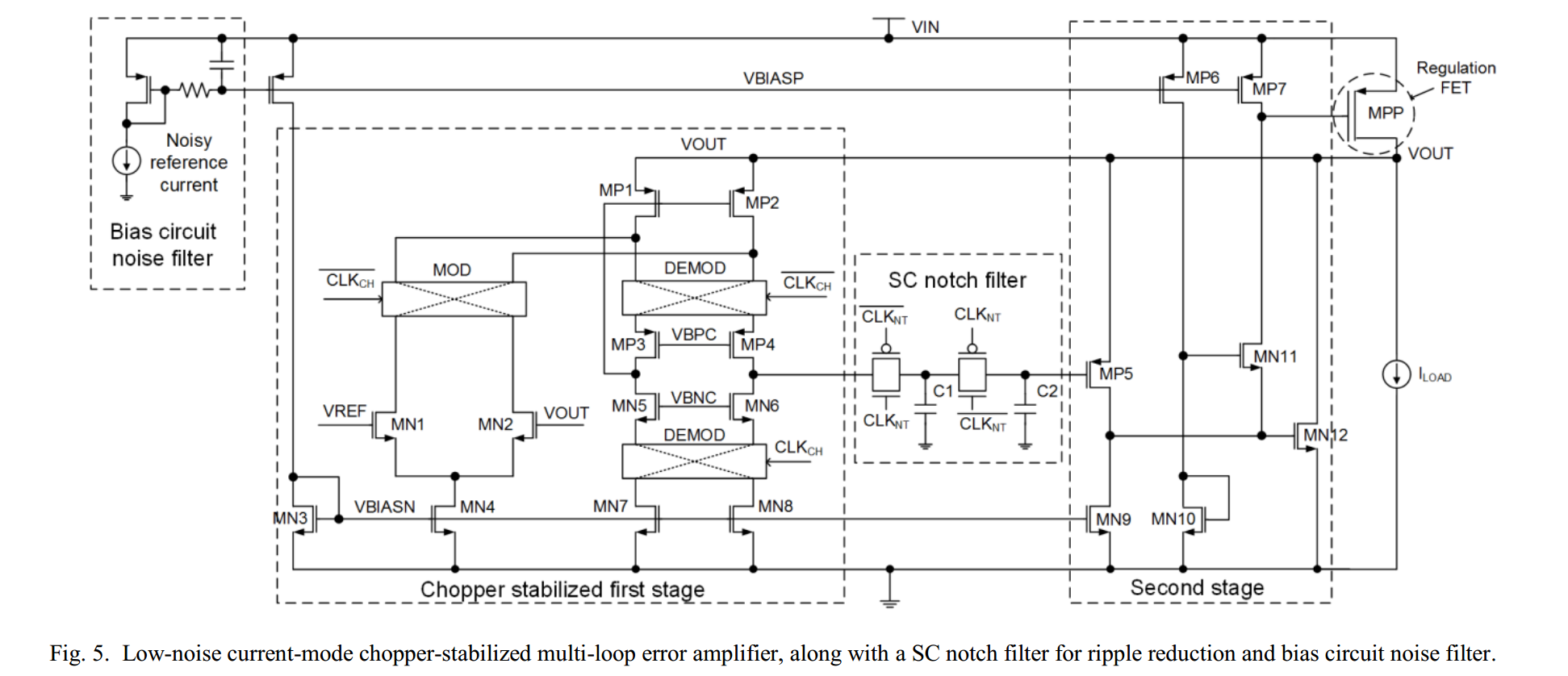

这里第一级时 Folded Cascode,主极点就在第一级的输出,Unite-Gain-Bandwidth = 20KHz。输出级就是 Ivanov 的那个 unconditional-stable 的输出级(似乎可以理解为一个 Super source Follower,这部分内容可以详见 CDR-OPA-POWERMANAGEMENT.pdf 的最后一章)

Chop Frequency 远高于 UBW,选择了 200KHz。第一个 Chop 没有放到 input pair 前面是因为 VREF 是 LPF 上 Hold 住的浮压,DIFFUSION 一旦引入就会导致 Leakage 问题,因此这里没敢去放开关,这样导致了 Input Pair 的 Flicker Noise 会主导;

Chop Ripple 通过 90° 位移的 Notch Filter 滤除。C1 = 5pF,C2 = 10pF,C2 更大似乎是为了缓解 Clock Feedthrough,这个 SC-Notch-Filter 效果是有的,直接把 200K CHOP FREQUENCY 的 Ripple 从 100uV 降低到 6.98uV 了

整个 EA 是放到 Power / Regulation FET 下面的,这样其实有助于提高 PSR;以此会带来启动速度较慢的问题,这个 Regulation FET 的 GATE Clamp Voltage 似乎可以通过几个 Diode 电压给一下,启动了之后再切换给 EA 控制。

However, this could result in a long startup time for the LDO due to self-regulation of its supply voltage. To avoid this, a clamp is used to ensure proper gate voltage at the gate of the regulation FET MPP during startup so that output voltage increases initially until the error amplifier turns on and starts regulating the LN-LDO output.