¶ 1 Overview

这篇笔记 Overview 了两种常用的OTP结构的经典论文,回顾了 One-Time-Programable Fuse 的发展历程

- 论述的 eFuse 是基于 Silicide Poly Resistor,编程后阻抗提高,其烧写机理分别是 Electromigration 和 Aggomeration;

- 论述的 anti-fuse 是基于击穿的,变成后阻抗提高,因此取名为 anti-fuse;其击穿的电介质从早年的 Amorphous Silicon、Oxide-Drift NMOS,到后面的标准工艺下的NMOS;值得细读是韩国科学院 KAIST 的 3-Transistor Cell,从2003年的第一篇文章,到2006年的JSSC,应该是较完整地实现了 Standard CMOS Process 下的 anti-fuse 设计

无论是哪种机制的机制的 FUSE,如果要自己设计熔丝,都需要明白其烧写机理,烧写前后的IV特性,以及烧写前后的可靠性问题。笔者理解,机制与电路实现难度并不算太高,但是与工艺特性高度相关,需要大量基于工艺的数据才能设计出可靠性 OTP,因此很多SOC设计公司会直接使用FAB的IP而非自己设计,当然也会对于模拟芯片设计公司或者志在全品类的芯片设计公司,也会亲自亲子设计OTP,以下这些论文也绝大多出来自于规模较大的芯片设计公司。

¶ 2 eFuse Electromigration

Electrically Programmable Fuse (eFUSE) Using Electromigration in Silicides, 2002

这一篇论文的引用非常高,来自于 IBM 公司 eFuse 的工程师/学者。

ELECTROMIGRATION has been studied widely to explain the failure of metal lines in microelectronic devices. Silicides are thought to be more robust than metals with regard to electromigration, resulting in their widespread use as local interconnects and in contacts to p and n diffusion regions.

金属硅化物(Silicides)应该是非常常用,这里解释了 contacts 使用 silicides 的原因。

A typical implementation is a laser-fuse, where laser energy is used to evaporate metal links and the resulting resistance change is sensed using a latch. This device pitch is not scalable below the wavelength of the laser beam, typically 1.06 m, resulting in excessive use of chip area.

这里解释了 Laser-Fuse 面积做不小的原因,Device 的宽度 (Pitch 通常可以理解为尺寸/宽度) 不能小于 激光的波长;而且我们希望封装之后再去 Program 而非封装之前。

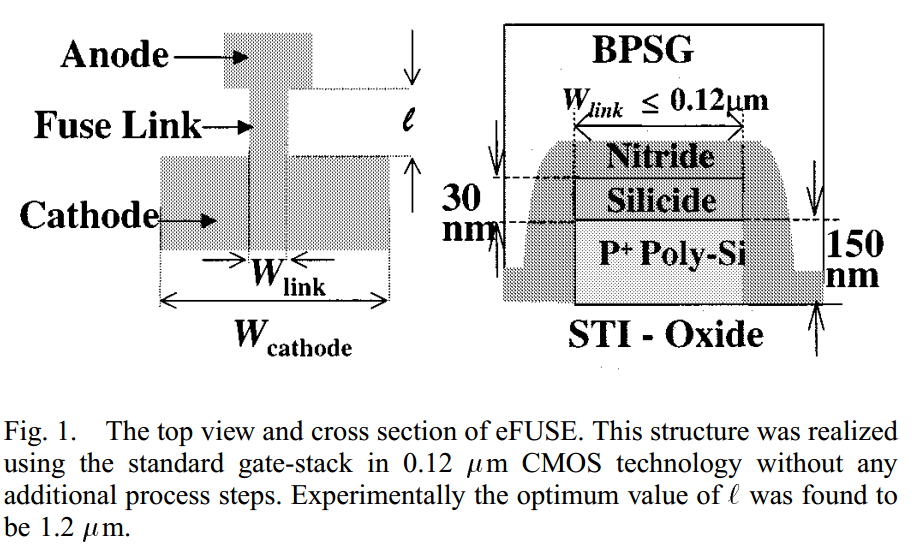

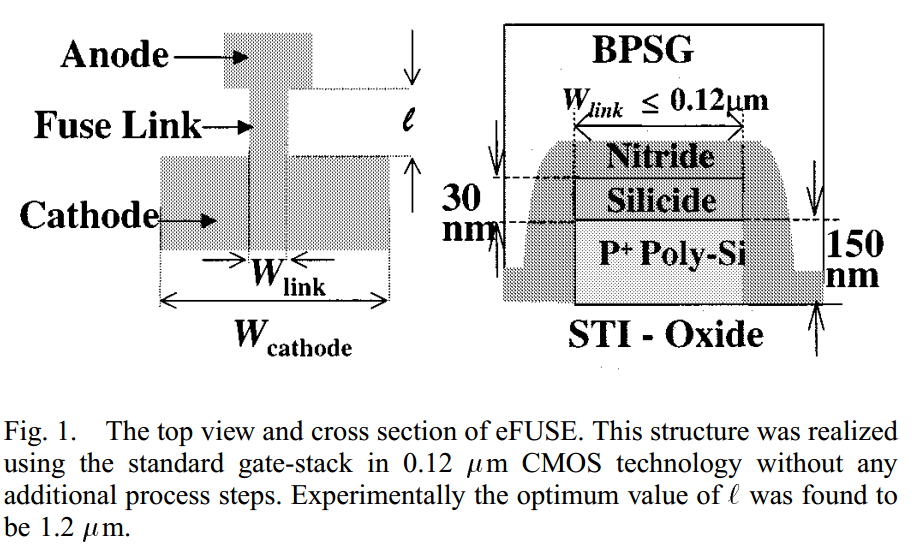

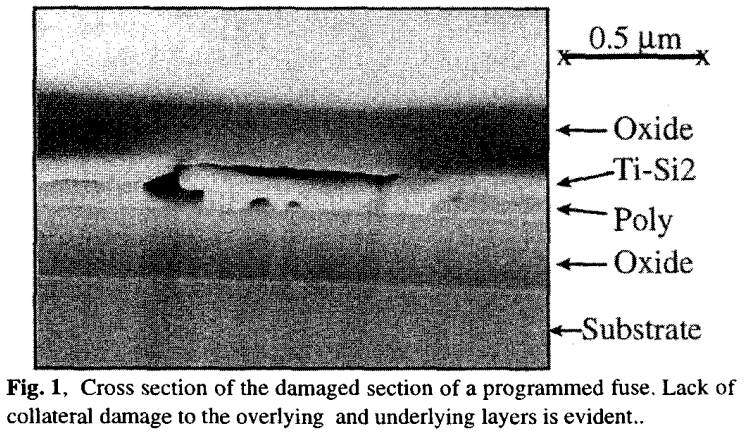

Fuse 的基本结构如下

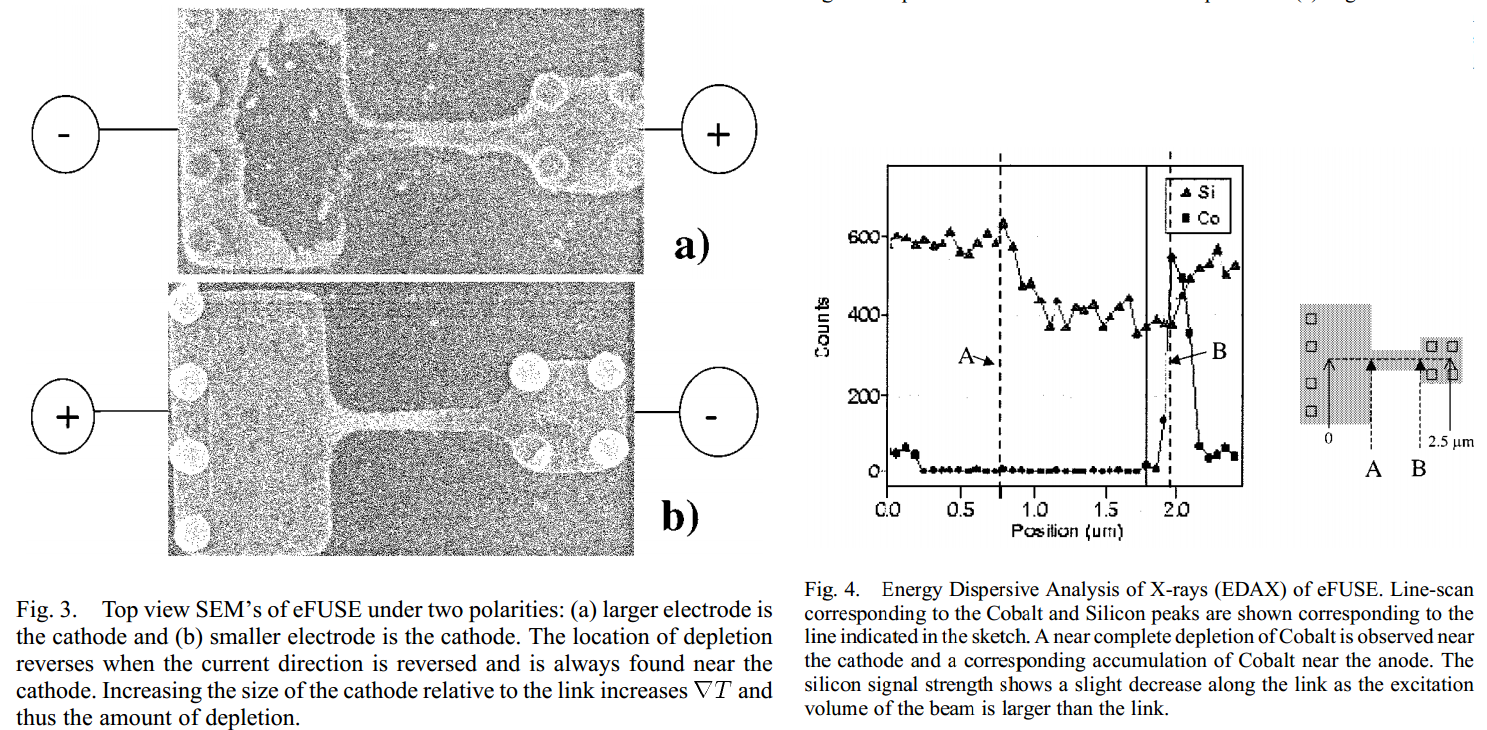

通过 SEM 和 Energy Dispersive Analysis of X-rays (EDAX) of eFUSE 证实确实发生了电迁移

扫描电子显微镜(SEM)是一种介于透射电子显微镜和光学显微镜之间的一种观察手段。其利用聚焦的很窄的高能电子束来扫描样品,通过光束与物质间的相互作用,来激发各种物理信息,对这些信息收集、放大、再成像以达到对物质微观形貌表征的目的。新式的扫描电子显微镜的分辨率可以达到1nm;

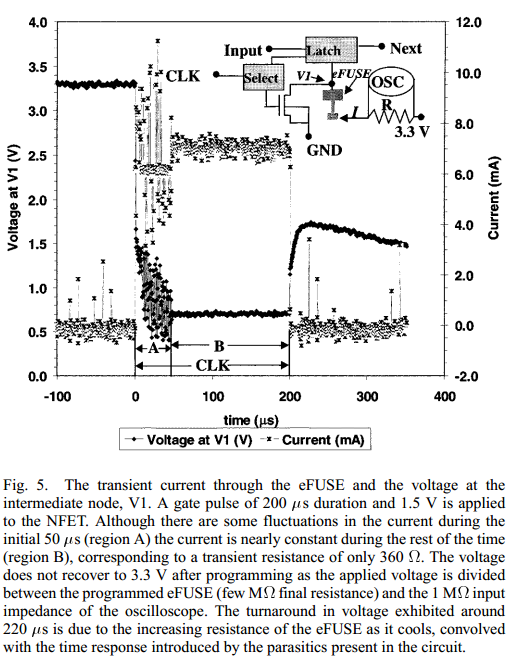

观察烧写过程中的电流和电压如下

瞬态数据显示,通过eFUSE的电流虽然在最初的50us(区域A)期间变化,达到峰值 10mA,但在接下来的150us(区域B)期间几乎是恒定的。 B中的链路电阻在360Ω处几乎恒定,并且低于最终的直流电阻。 这归因于在连接处实现的高局部温度,估计在这些温度下为850°C的量级,多晶硅呈现导电,被理解为在具有大量的本征载流子浓度的情况下导电。 B中的这种低电阻状态允许eFUSE从电源耦合电流更长时间,从而增加电迁移的物质以及增加最终的电阻。

编程后电压不会恢复到3.3V,因为施加的电压在编程的eFUSE(MΩ级的最终电阻)和示波器的1M输入阻抗之间分配。 在220us附近显示的电压变化是由于eFUSE在冷却时电阻增加,与电路中存在的寄生效应引入的时间响应有关。

Other modes of increasing the resistance of a poly-silicide links such as thermal rupture or agglomeration [2] do not exhibit consistent behavior and were found to be unstable with thermal cycling. The high final resistance achieved by electromigration also prevents the coupling of significant current during sensing preventing any reversal of programming.

从IBM的论述中,之前基于Intel 的基于 Agglomeration 方案 似乎有些瑕疵,这里的 [2] 就是 A PROM Element Based on Salicide Agglomeration of Poly Fuses in a CMOS Logic Process, 1997

接下来需要理解如何发生 电迁移,需要从物理层面上理解

- 表示 迁移粒子(原子、离子等)的通量,flux of migrating species 翻译为迁移粒子

- 原子密度

- 扩散系数,随温度变化,写作

- 绝对温度

- 迁移粒子的有效电荷

- 玻尔兹曼常数

- 局部电场向量

这个公式说明,在有电场和扩散存在的情况下,带电粒子会受到力的作用而产生净迁移。迁移通量 越大,原子越容易移动,从而在微观尺度上导致电迁移现象,比如粒子(material 这里翻译为粒子)空洞、堆积,最终实现熔丝断开。

表示:要发生电迁移,必须有迁移通量的“非零散度”,即迁移物在某个点净流入或流出,才能导致材料累积或空洞,从而实现熔丝编程。产生这个效应的机制有两个:

- 温度梯度()

- 晶体结构变化引起的扩散系数变化()

文中指出,第一种方式(温度梯度)更可控,可以通过设计器件几何形状和功耗来人为控制。文中提到一个实际例子,在 eFUSE 结构中,阴极(Cathode)区域设计得比中间连线(link)区域大, 这样会导致在阴极与连线之间形成一个更大的温度梯度(),热量从发热点(如 link)向两端阴极或阳极传导,因此中间会形成高温中心、温度梯度向两端递减的状态。这有助于形成迁移流密度差异,从而促使中间 link 区域原子迁移断裂。

通过实验,确定了最佳尺寸为

以上大概率是几何和热耦合驱动的普遍规律,至少在 Tungsten Silicide (钨硅化物)的 link 也发现了相似的特性;这篇 IBM 的论文从 EDAX 显示使用的是 Cobalt Silicide (钴硅化物)

公司工艺同事口头确认,90nm 到 180nm都是 Cobalt,从 Comparison of transformation to low-resistivity phase and agglomeration of TiSi2 and CoSi2,1991年的这篇文章看到,相比TiSi2,CoSi2工艺略复杂,但是与工艺线宽相关度更低(575°C ~ 850°C furnace annealing 炉内退火不会发生 agglomeration),侧面证实了工艺同事的信息。

¶ 3 eFuse Agglomeration

A PROM Element Based on Silicide Agglomeration of Poly Fuses in a CMOS Logic Process, 1997

同样这篇论文的引用也很高,来自于 Intel 公司 eFuse 的工程师/学者。agglomeration 意为团聚、聚集,在材料学中指材料在高温下粒子迁移、结块,导致结构不连续或局部变薄。

In our structures, post program resistance varied from several hundred Ohms to several hundred kOhms. Post program I-V characteristics are found to be nonlinear and therefore, the value of resistance varies with applied bias.

说明烧写之后的阻抗之后是非线性的

Ti-silicide films resulting in sheet resistance ranging from 3 to 4 ohms per square have been studied

Ti-Silicide的方块阻值大约是3~4Ω

Silicide imperfections are more likely for long narrow elements and best silicide lines were found to be the ones made from p-doped poly.

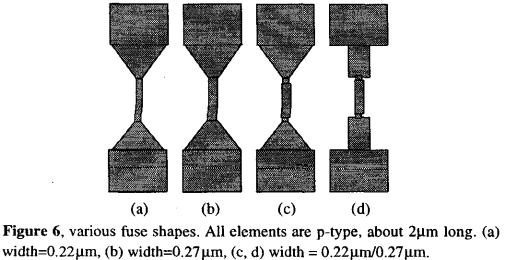

对于长窄的熔断器,硅化物更容易出现缺陷。而掺p型杂质的多晶硅制成的熔断器硅化物质量最好。

文章对比了四种结构,最后发现 (c)(d) 结构比较好,但是当时他们适用了 thermal simulation 的方法,target 是让温度达到 800°C 以上,这个差不多就是 silicide 发生 agglomeration 的温度。这里我们只是知道了他们会用 simulation 的方式与 实测去印证,具体我们在用时,由于工艺的细节不一样,还是应该因地制宜,这里不再去花时间理解他们当时的细节。

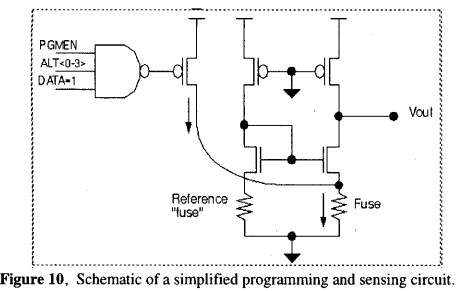

Sensing Circuit 如下,应该平平无奇,就是用一个 Common-Gate 的比较器,重要的还是要去选择这个 Reference “Fuse” 取多大

¶ 4 anti-Fuse Amorphous Silicon

Improved Reliability of Amorphous Silicon Anti-Fuse Used in High Speed FPGA, 1994

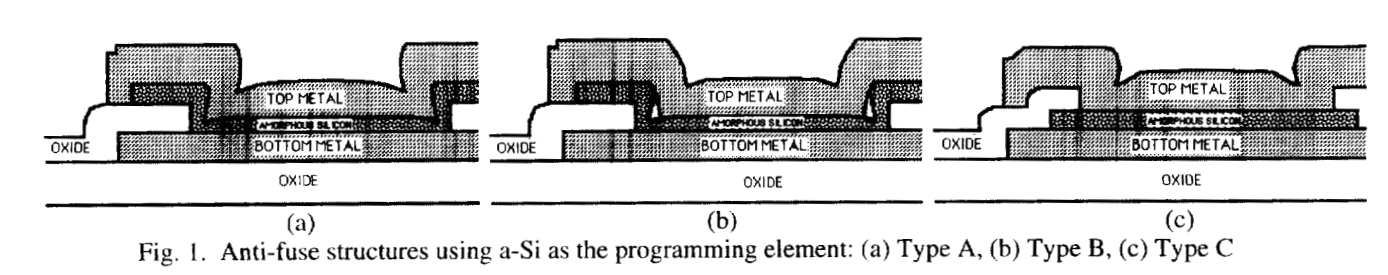

文章来自于 VLSI Technology 是一家美国硅谷的半导体公司,1999年被 NXP 收购。文章对比了三种 非晶硅 的反熔丝结构的编程电压,失效率和可靠性。

下面这段说明了这种 anti-fuse 的烧写方式

For the programmed (On) resistance, the anti-fuse is first programmed with a 14V pulse applied for a duration of 1.5msec (programming current - 20 mA).

PECVD 全称是 Plasma-Enhanced Chemical Vapor Deposition(等离子体增强化学气相沉积)

这是半导体制造中常用的一种薄膜沉积技术。与传统的化学气相沉积(CVD)不同,PECVD 使用 低温 且通过 等离子体激发反应气体,从而在晶圆表面沉积一层薄膜(如氧化硅、氮化硅或非晶硅等)。由于温度较低,适用于温度敏感的材料或后段制程。

- Type A, 由于 PECVD 工艺的特性,在反熔丝通孔的角落以及通孔内部平坦区域,非晶硅(a-Si)会变薄。这个变薄会导致早期的失效,也会导致编程电压变低;

- Type B,在变薄的地方增加了 OXIDE 的填充保胡,让 早期失效率 (infant failure rate) 几乎降低到零

- Type C,应该是工艺顺序,先做 Bottom Metal,再做 A-Silicon,然后再做 OXIDE 和 TOP-METAL,这样会让 A-Silicon 非常的均匀,编程电压也变得非常一致。但是这样 sandwich 的结构在 thermal cycling tp 460°C 的实验中表现不好,作者认为是 This clearly indicates that it is not the local thinning of the a-Si in the via but the barrier integrity of the upper metal sandwich that degrades during the thermal stressing.

最终量产上选择了B结构。整体上这篇文章比较早,已经不是现在的工艺了,从这篇文章可以看到的是

- anti-fuse 在很早就是商用 OTP 方案了;

- 关注点在于 击穿电压、漏电和稳定性,已经 anti-fuse 的结构

- 击穿电压与 thinness 相关

¶ 5 anti-Fuse Oxide Drift NMOS

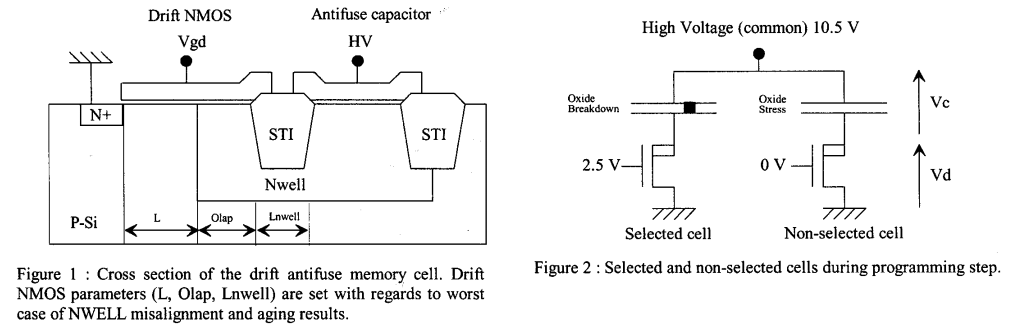

One Time Programmable Drift Antifbse Cell Reliability, 2000

ST Microelectronic公司,应该是最早发出来的论文,在CMOS工艺上利用栅氧击穿实现 anti-fuse

Owing to Nwell depletion and induced access resistance, this device can sustain high voltage on the drain for a limited stress time

要实现让 Gate 击穿,但是 Drain 不能坏的特性

The capacitor gate is N+ doped polysilicon rather than P+ polysilicon in order to reduce capacitor breakdown voltage. In fact for positive gate voltage the oxide electric field is larger due to work function difference with P+ polysilicon. Capacitor area and shape impacts will be discussed below.

这里解释了使用 N+ PolySilicon 可以降低击穿电压

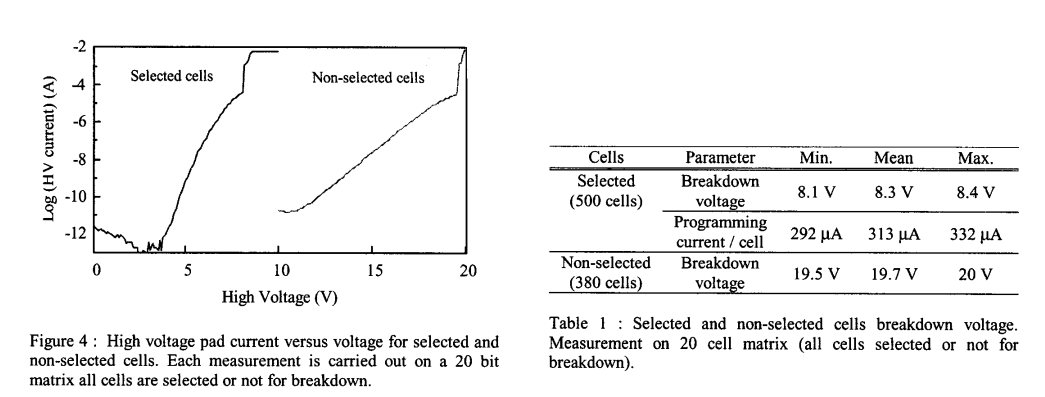

Selected Cell 的击穿电压与 Non-selected Cell 的击穿电压是不同的,文章显示最终选择了10.5V 50ms去完成烧写,测试了10V/10.5V/11V烧写,发现10.5V烧写可以达到100%的烧写成功率。

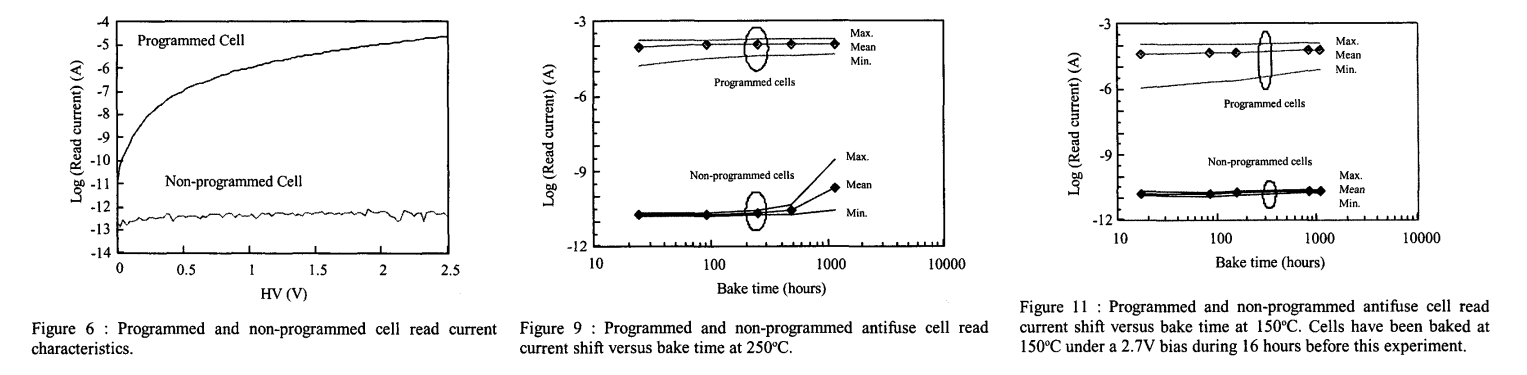

上图显示了 programmed Cell 的IV 特性,在 log(current)下仍然是高度非线性的;2.5V下读取电流达到25uA(10^-5,10uA量级);之后就是一些大家都会进行的的热循环测试去观察其稳定性,结论是挺好

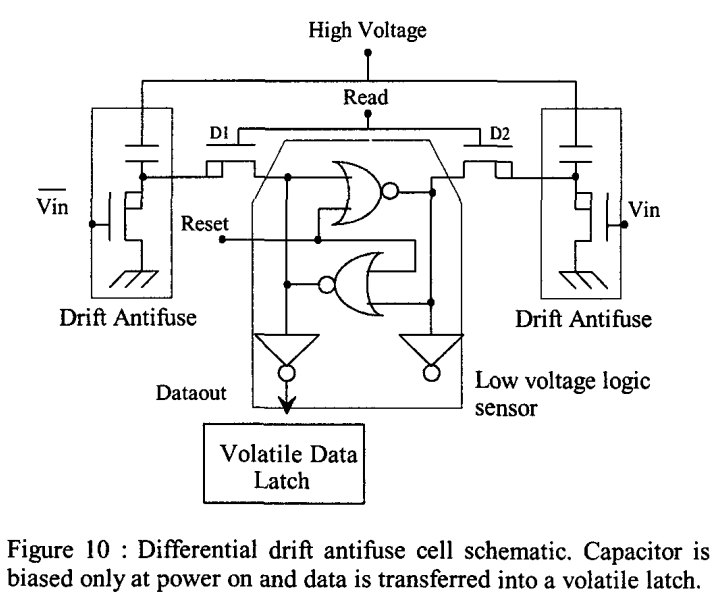

最终的读取电路如上,差分结构进一步增强可靠性,结合一个RAM去读取。

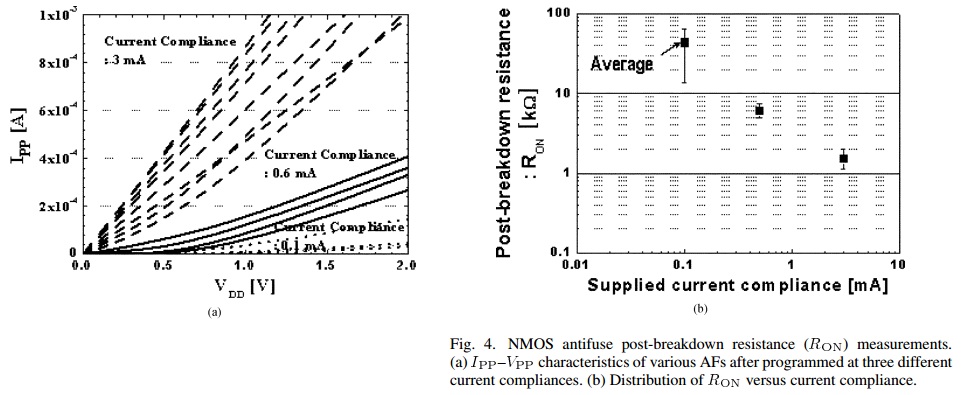

这篇文章还有一个有意思的公式,给出了最终 Programed Resistor 和 Programed Current的关系,烧写时的电流越大,最后的阻抗越低

¶ 6 anti-Fuse 3T Standard CMOS

Three-Transistor One-Time Programmable (OTP) ROM Cell Array Using Standard CMOS Gate Oxide Antifuse,2003

从某种意义上来说,这篇来自韩国科学技术院(Korea Advanced Institute of Science and Technology)的文章,最先给出了完整的 Standard CMOS 工艺下基于栅氧击穿的解决方案,6.5V的烧写电压,烧写时间为100ms,工艺为 0.18um Standard CMOS。

额外信息,待证实,这个工艺的 GIDL 承受的最大 Drain/Substrate 电压是 9.5V, 1s 以内不会坏?

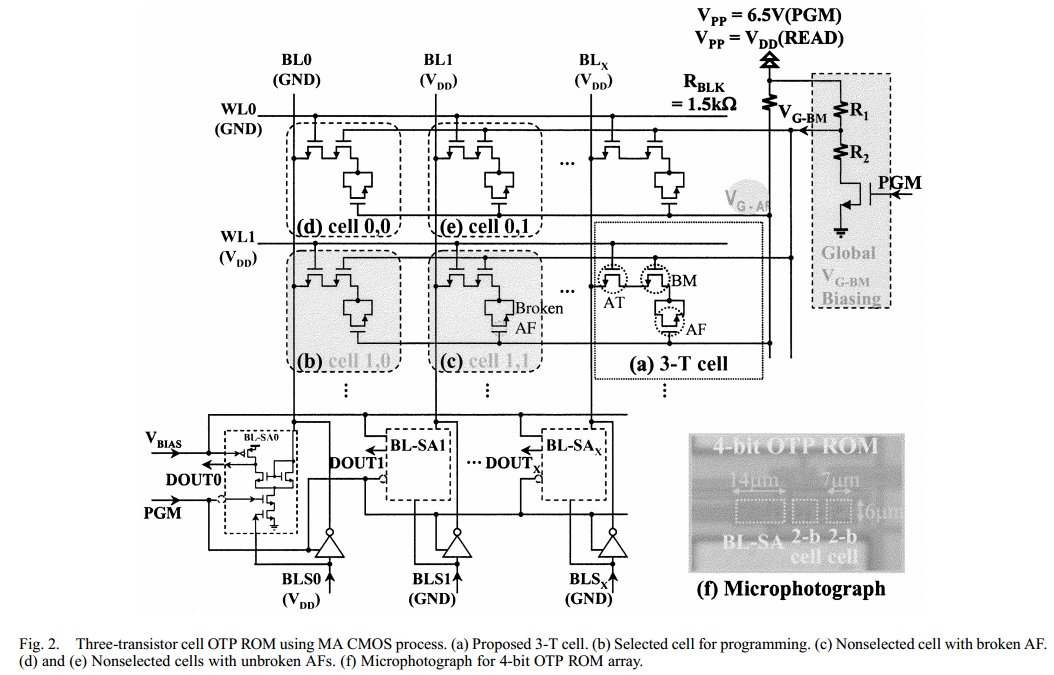

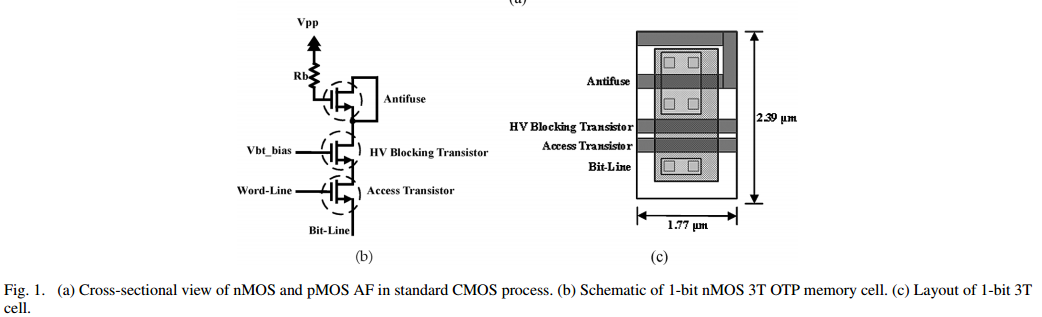

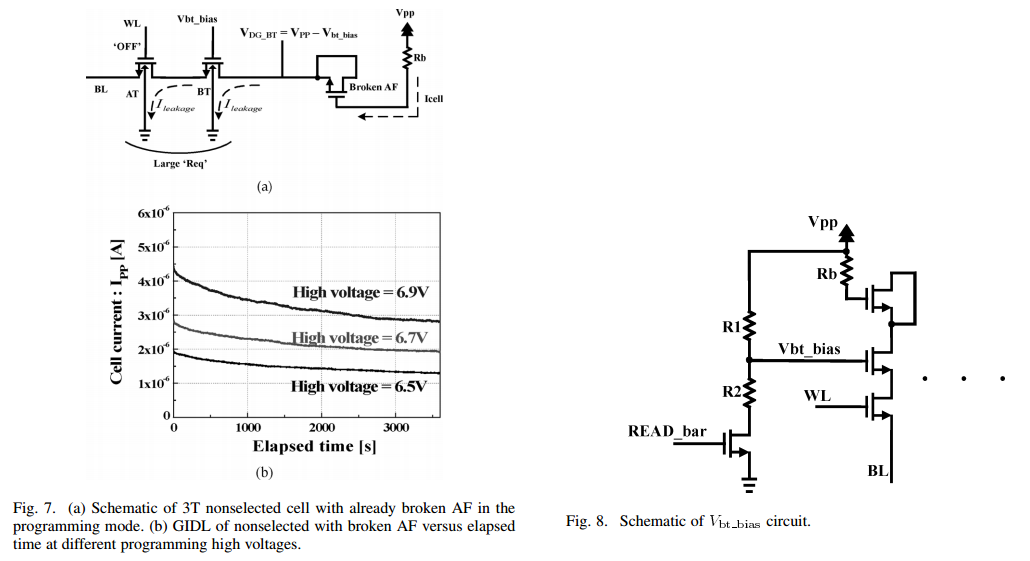

- (a) 给出了3T的结构,AF是NMOS Anti-Fuse;AT是 Access Transistor 其实就是选择管;BM是用于Block高压的Mosfet,在烧写的时候使用Vpp/2作为栅压,Read的时候接Vpp;接AF栅极上有一个1.5k的电阻用于限流

- BL0/1/2/x是列选,WL0/1/2/x是行选;BL0=GND以及WL1=VDD 意味着 (b) 这Cell 是当前被选中的

- 没有被选中的 (c) Cell,BM管的Drain是能够看到高压的,但是AT管处于 off-state 意味着只会有很小的 Gate Induced Drain Leakage (GIDL) Current 会从 Drain 流入到 Substrate。至少 0.18um 和 0.25um 工艺保证了即使长期处于这种偏置状态,器件也不会损坏;

- 至于没有被选中的 (d) (e) cell,高压会在由于AT和BM分压,而且BM管的VPP/2也很好地保护了AT管。在这样的情况下,未被选中的 AF 的击穿电压会超过10V,而烧写电压选择了6.5V,因此也是安全的

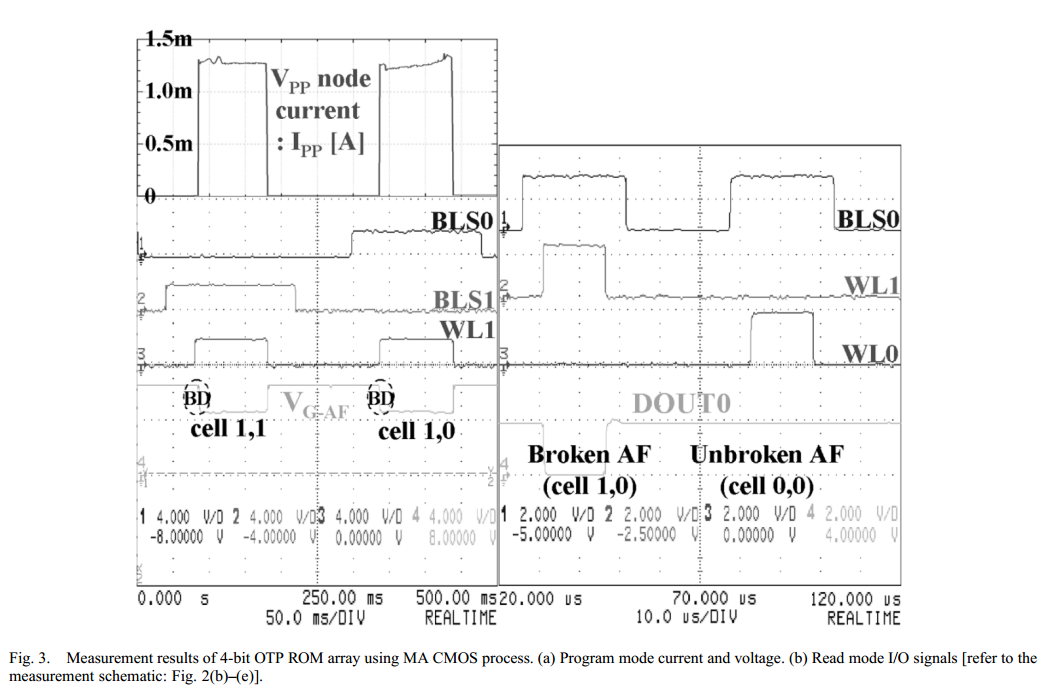

烧写发生击穿后,AF栅电压从6.5V的烧写电压,在1.3mA以及1.5K限流电阻的作用下,变成了4.7V,从下面这个图看到烧写时间是100ms

¶ 7 anti-Fuse Toshiba pure CMOS

Pure CMOS One-time Programmable Memory using Gate-Ox Anti-fuse, 2004

来自 Toshiba Corporation 公司的文章,这篇文章更多的地,是讲了了一些原理。至于读取电路,也是做了个基准,由于是纯数字芯片,没有用 IR 产生基准,而是用了 Charge-Sharing 的方式给出

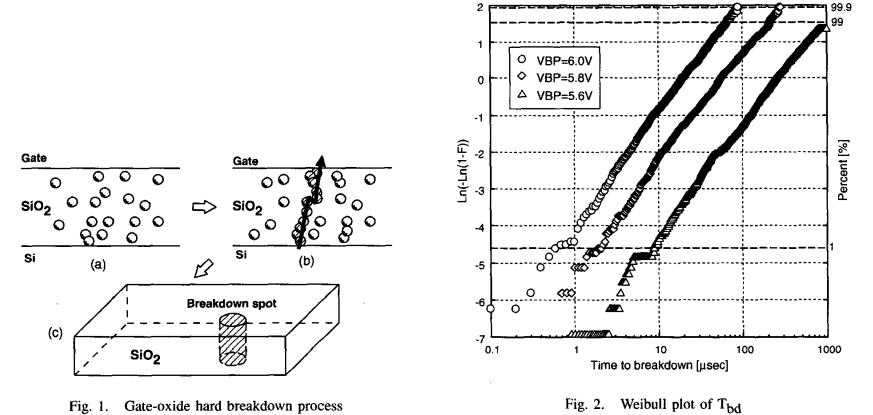

上面这个图,文章描述击穿过程分为 (a)(b)(c) 三个阶段,刚开始有 defect,当 defect 数量达到一定数量后,形成 Breakdown spot;从第二个分布的图中,看到仅仅需要 1ms 的时间,分布概率就可以达到 100%,文章所用的工艺,90nm standard CMOS Process,1.8nm-oxide-thinkness,击穿之后的限流为 2mA

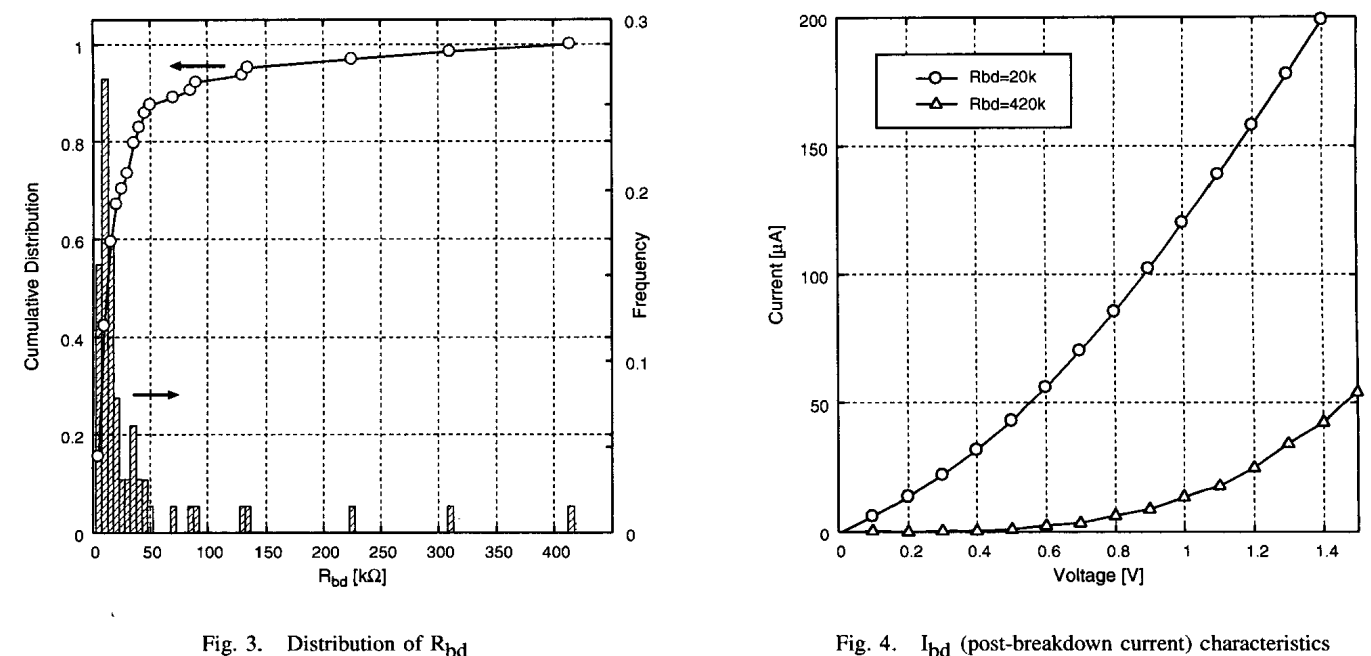

Fig. 3 shows the cumulative distribution of post-breakdown resistance (Rbd), where Rbd is defined at 0.5V bias of VBP

The mode of Rbd was 20kΩ and the maximum was 420kΩ.

Fig. 4 shows the post-breakdown current characteristics. The data indicated with circles were measured from a sample with the mode Rbd. The data measured from a sample with maximum Rbd are plotted with triangles and show a diodelike characteristic. It is considered that the difference is due to the location of the breakdown spots [6]. If the breakdown spot is located in the gate-source/drain overlap region, the gate current would behave ohmic. When the breakdown path is formed in the channel region, the breakdown spot may act as an additional drain, then the gate current characteristics would resemble that of MOS transistor.

上面这一段显示,如果击穿位置发生在 Gate - Drain/Source Overlap 区域,表现为 Ohmic 特性,圆圈的IV特性;如果击穿位置发生在 Channel,则表现为 Diode-like 的IV特性;

¶ 8 anti-Fuse 3T Standard CMOS 32KB JSSC

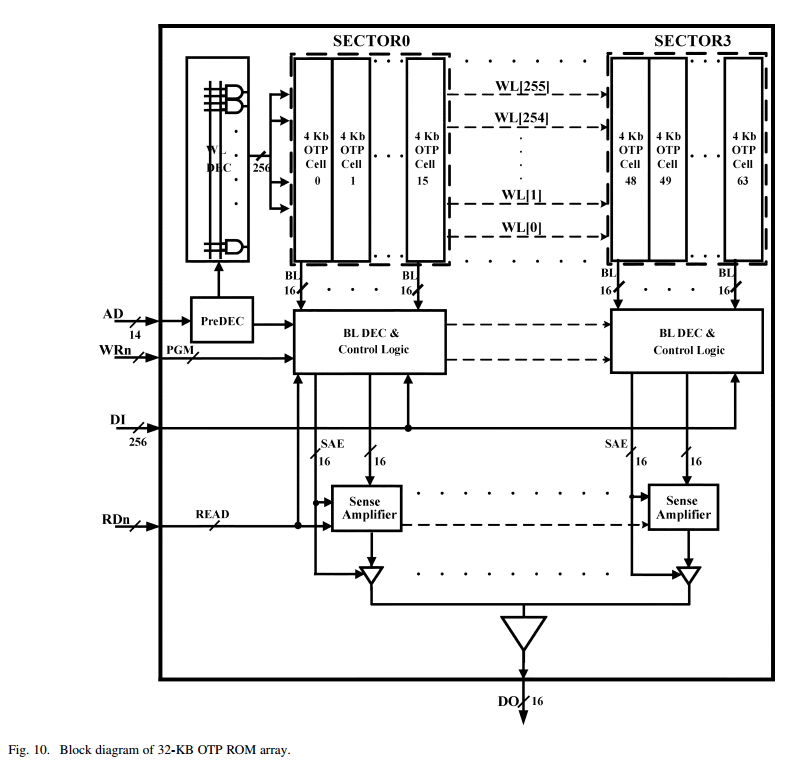

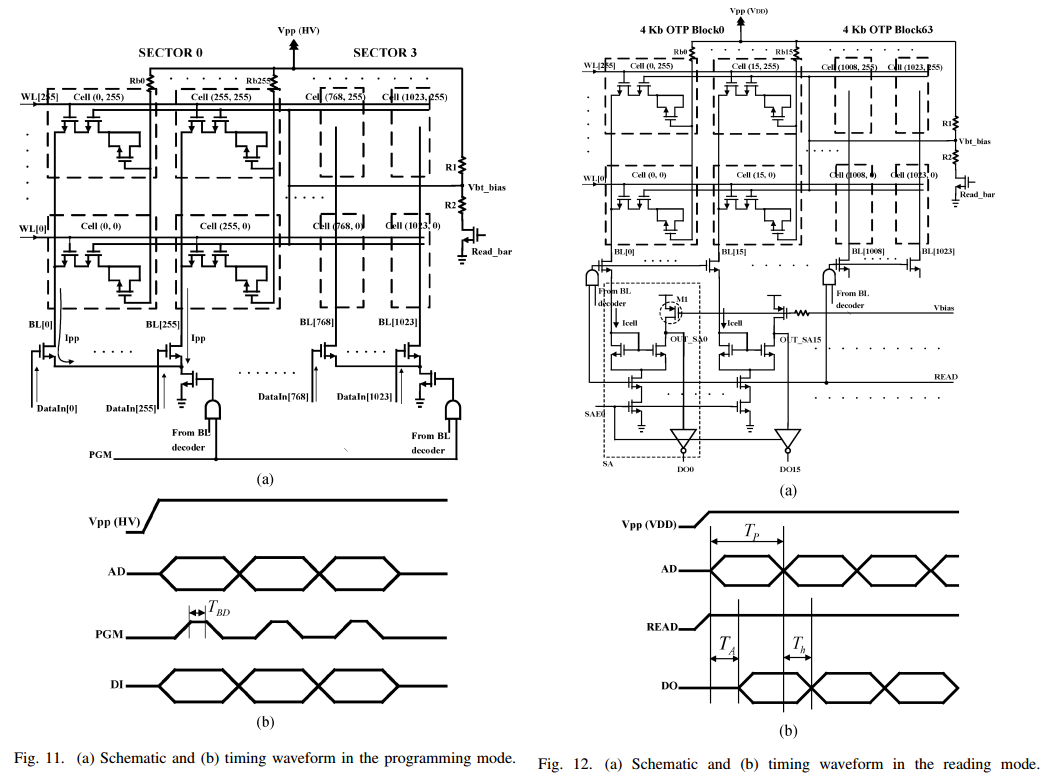

这篇应该是韩国科学技术院(Korea Advanced Institute of Science and Technology)2003年那篇短论文的续集,做了一些优化,而且实现了大规模阵列的处理,32KB = 32 * 1024 byte = 32 * 1024 * 8bit = 262144bit,这篇篇幅较长,内容比较详细

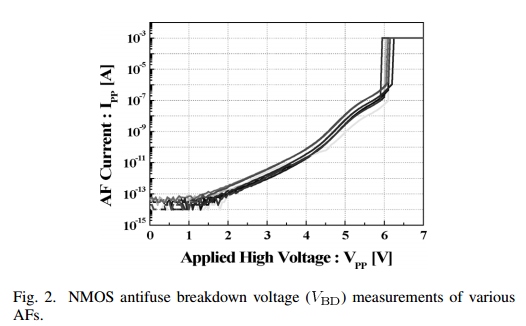

工艺是 1-poly 6-metal 0.18um standard CMOS process, Tox=40A,击穿电压在6V左右

给出了版图,这个版图是定制的,左边的 schematic 只是抽象出来的

In accordance to the measurements, the average value of TBD is 5.9 ms with the standard deviation of 3.7 ms. CC and VPP are set at 1 mA and 6.5 V, respectively

显示用于测量击穿电压/击穿时间,以及击穿后的后的电流如上。

这个图同样给出了,不同的击穿后的电流,阻抗特性是不一样的。最终论文选在600uA附近的击穿电流,猜测考虑到大规模阵列的问题,因为按描述,要一次性烧写 32 bytes !

It has a 32-byte page write mode where 32 bytes of data is programmed simultaneously in a single program cycle. In the reading mode, the 16-bit data is outputted through the sense amplifiers in the output path.

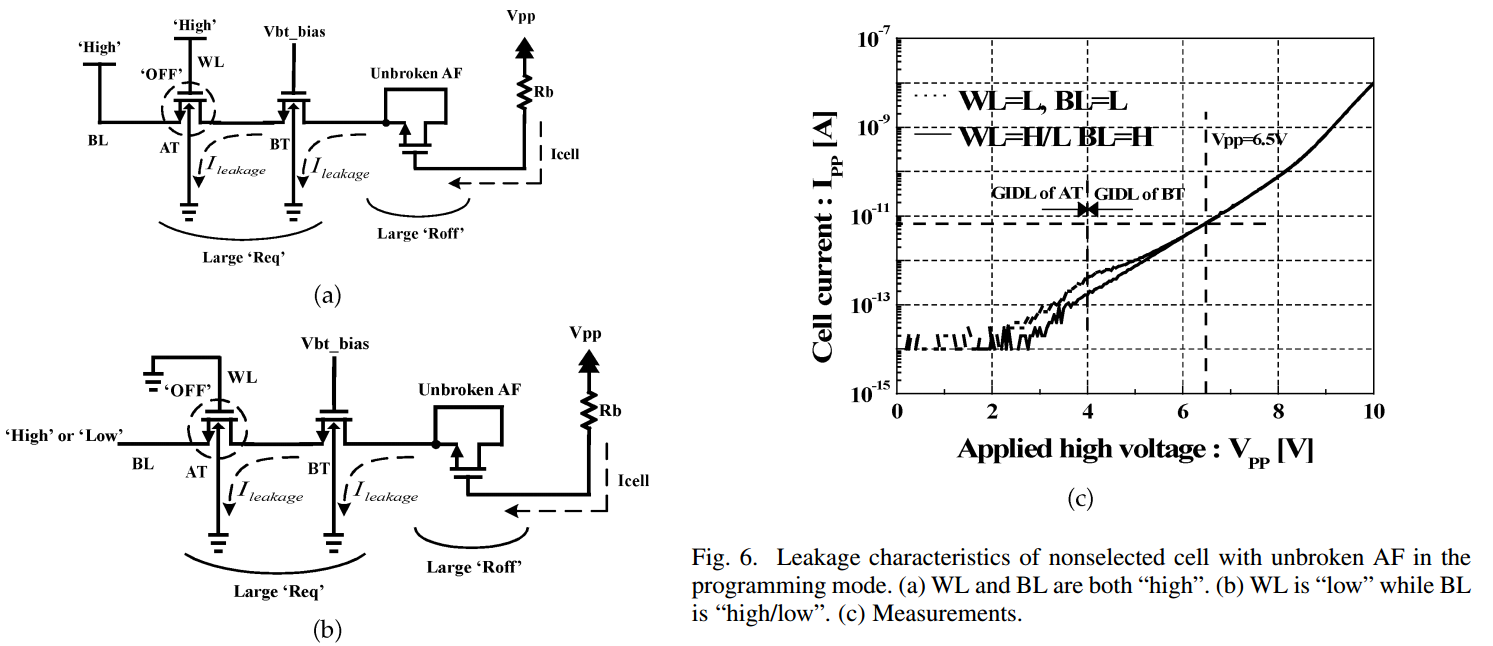

对于没有被选中的管子,(a)是BL电压为高没有选中,(b)是AT管为低没有选中,这两个 AF 都不能被误烧写,防止误烧写的前提就是不能让 AF管的 Gate-to-Source/Drain 看到高压。但是 Leakage 电流会让本该相等的 栅压/源漏电压不再相等,我们需要评估这里的电流。

- (b) 随着VPP电压的上升,先出现 AT_GIDL_CURRENT:个人理解这里的BT的栅极电压Vbt_bias=Vpp/2,BT_VGD的电压要比AT_VGD小,所以是最先有AT_GIDL_CURRENT;

- 之后AT_VG 电压也高到可以导通 AT 管,此时 AT_VD 和 AT_VS 电压将保持一致,直到 AT_VGD < Vth 后,BT管将被关闭;

- 当Vpp电压高于5V后,两者的电流将会相等,因为此时是BT_GIDL_CURRENT主导

对于未被选中的,当时 Broken-AF 的Cell 来说,此时 BT-VD 的电压就是直接的高压,如果 Vbt_bias=1.8V,编程电压未6.5V是,此时 BT-VGD=4.7V,文章作者说了通过可靠性分析,这样的VGD不足以造成可靠性问题。当时为了更加可靠,可以使用 Vpp/2 作为 Vbt_bias,这样BT管的压力会小很多。

对于烧写过程:因为阵列是 32KB,即使 GIDL 电流小 (uA量级),262,144 bit 下总的漏电也是很大,这样会产生巨大的IR-DROP,让最终加载在AF管上的Gate-to-Drain/Source 电压不那么高;其次因为一次性要烧写 32 Byte,也就是256bit,每个烧写电流为600uA,20ms,意味着150mA的烧写电流;为了缓解这些电流压力,需要多路径多PAD多分区。

对于读取过程:读电路做到了1.8V,Ron=500K在10M的速率下读取,每次读取16bit,这样的速度还是很快的;我图中看到读取电路也就是一个基于 REF-CURRENT 的电流比较器。

¶ 9 GIDL/DIBL/Subthreshold-Leakage

GIDL, Gate-Induced Drain Leakage

GIDL 电流是指 在栅极偏置为低电压时(通常为0V或负电压),漏极偏置为高电压时,由于栅-漏之间形成强电场,在漏极区附近的耗尽区中发生的带间隧穿(band-to-band tunneling) 而产生的漏电,产生位置在 NMOS 的漏极-栅极重叠区域(drain-edge under gate)

带间隧穿(Band-to-Band Tunneling, BTBT)是主要的物理机制,在高电场作用下,漏极处的价带电子会直接穿越禁带隧穿到导带中,产生电子-空穴对:电子进入漏极 → 构成电流;空穴进入衬底 → 增加次级效应(如阈值电压漂移)。这种机制类似于 ESD(静电放电)或高场击穿中的隧穿机制。

造成的影响如下

- 静态功耗增加:在电路“关闭”时本应没有电流流动,但 GIDL 导致静态电流泄漏 → 增加待机功耗

- 电路老化 & Hot Carrier Injection (HCI) 协同:GIDL 会在漏极附近形成强电场,促使载流子获得较高能量,可能造成热载流子注入(HCI)和间接引发栅氧击穿(oxide wear-out)

- 电荷捕获,影响阈值电压 (Vth) 漂移:GIDL 产生的空穴进入衬底,可能被俘获在界面陷阱或氧化层中,导致Vth 变化,器件特性漂移和时序不稳定

- 对 LDMOS 或高压器件影响更严重:在高压模拟/功率CMOS中,GIDL 是器件退化的一个主要因素

Drain-Source Subthreshold Leakage

当 MOSFET 处于“关断”状态(即 VGS < Vth),但 VDS 很大时,即使没有形成导通通道,还是会有少量电子从 source 热激发穿越至 drain

DIBL, Drain-Induced Barrier Lowering

高 VDS 会降低栅下的势垒,使得 VGS 虽然没有超过阈值,channel 还是导通了。导致 Source 到 Drain 出现漏电,即便 transistor 本该是关的。在 传统长沟道 MOSFET 中,栅极主导控制沟道的电势。漏极的高电压会“扩散”其电场到沟道区(特别是栅下靠近 drain 的一端),这导致沟道势垒降低(即使 VGS 不够大)、电子更容易从 source 越过势垒流到 drain、晶体管提早导通,Vth 变小。

总结两者的区别

- GIDL:Drain 在高压,Gate 在低压,漏极下方的耗尽区形成 强电场 → 带间隧穿,电流流入 bulk(substrate)

- DIBL:漏极电场“侵入”沟道,把源极侧的能垒拉低,等效降低 Vth,让 device 更早导通