对于一个差分信号VIN=VP-VN,在一个CHOP CLK周期内:

(1)上升沿时,原来冲到(VN-VCM)的电容,接到信号源(Postive端)了,需要给该电容充一次电,从VN充到VP

(2)下降沿切换到另一个电容,状态还是(VN-VCM),充到(VP-VCM)次电,所以是2CV

所以输入阻抗:差分输入电压/单端平均电流(ADI前测试工程师计算方法),输入偏置电流确实在ADI的书中有明确定义(文末),按照这种测试方法,推导出的输入阻抗公式与Qinwen Fan书中的定义是一致的。

由于输入端接的是下级板(M3-SUB),有一些对地电容,但这个应该不是主要的寄生电容(估算只有千分之5),似乎输入端chop开关后的所有寄生电容有30%(有待后仿或者分析版图布局去验证这个猜测)?fchp=1MHz/4=256KHz,从增益2开始有Postive Feedfoward Loop的输入阻抗boost效果,Huijsing课题组的Qingwen Fan(南开大学,Delft大学)的书上写着大约可以提高10~20倍(受限于mismatch),这里按照15倍计算。

基于以上假设,某款芯片 CCIA 估算结果与实测较接近:

| Gain | Cin | R=1/(2*Cin*1.3*fchp) | PFL*15 | 实际测试MΩ |

|---|---|---|---|---|

| 1 | 1.8pF | 0.834669 | - | 0.727537 |

| 2 | 1.8pF | 0.834669 | 12.52003 | 11.65501 |

| 4 | 3.6pF | 0.417334 | 6.260016 | 8.576329 |

| 8 | 3.6pF | 0.417334 | 6.260016 | 6.925208 |

| 12 | 5.4pF | 0.278223 | 4.173344 | 4.347826 |

有一个很有意思的问题,电容耦合的放大器/积分器,输入电容是CIN,不需要考虑CF;而输出端的等效电容确是两者串联CIN*CF/(CIN+CF);尝试直观解释如下:

- 从输入端观察,激励在输入,交流信号经过CIN后加载在放大器的输入端,放大器通过CF的负反馈,使得放大器的输入点成为虚地,因此信号CIN的另一端是地;或者认为跨接在【反向+高增益下】放大器的电容CF,在输入端可以看成是米勒电容,因此在放大器输入端看到的CF电容实际是ACF,CIN与ACF的串联结果还是CIN。

- 从输出端观察,激励在输出,此时放大器没有反馈能力,因为他的低阻输出被理想信号源激励淹没了,此时放大器的输入端就仅仅是一个浮空点,因此从输出端看到电容是CIN和CF的串联。

- 当然,最笨的办法,分析小信号模型,求解KCL/KVL方程,也可以得到相同结论。

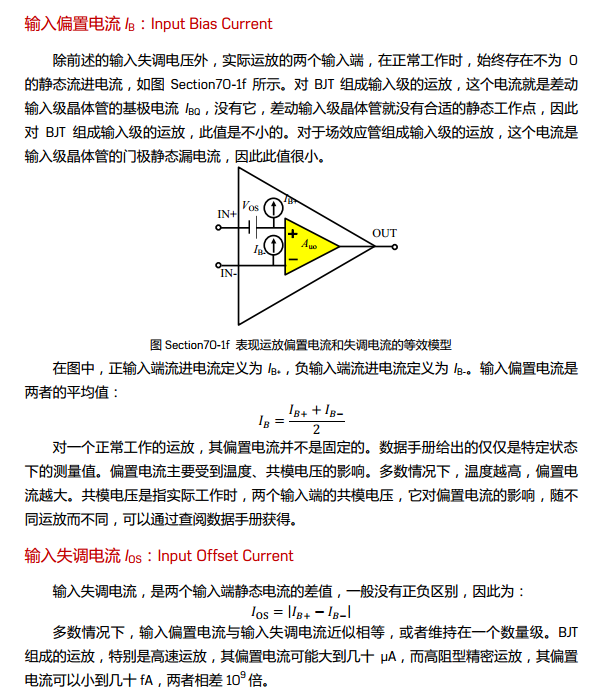

ADI《新概念模拟电路》对输入偏置电流的定义(截图)