参考文献:A 19 nV/√Hz Noise 2-μV Offset 75-μA Capacitive-Gain Amplifier With Switched-Capacitor ADC Driving Capability

¶ 1 设计思路

¶ 1.1 隔直电容后偏置设计

电容耦合放大器输入共模不能通过自身反馈建立(因为电容隔直),需要额外的偏置电路

(1)传统做法是放一个大阻值的输入偏置电阻,阻值较大是为了噪声考虑?问题是输入共模建立时间太慢了?而且会引用线性误差如果偏置的不合适。

(2)Switched Capcitor偏置

(3)另外一种做法是 CM Cancellation

H. Chandrakumar and D. Markovic, “A 2.8 μW 80 mVpp-linearinput-range 1.6 GΩ-input impedance bio-signal chopper amplifier tolerant to common-mode interference up to 650 mVpp,” in ISSCC Dig.Tech. Papers, Feb. 2017, pp. 448–449.

(4) 输入共模采样CMS,也就是这篇论文的这做法

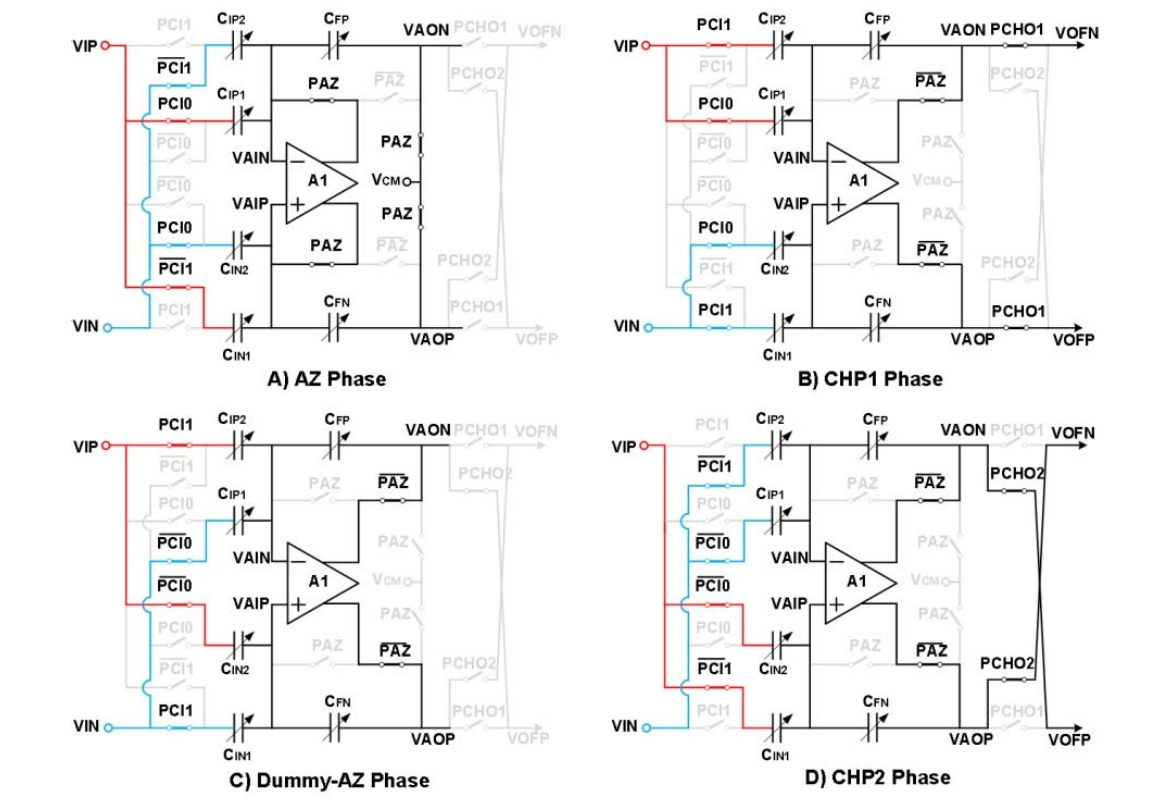

这篇是AZ+CHOP+CHOP GM1的方法

A) AZ阶段:

- CIP的两个电容一个接正,一个接负;CIN的两个电容一个接正,一个接负;

- 断开GM2,CF由“GM1单位增益反馈”和“CMFB”驱动;

B) CHOP1阶段:

- CIP的两个电容两个都接正;CIN的两个电容两个都接负;

- CF由GM1+GM2的差分输出驱动;

C) Dummy AZ阶段:

- CIP的两个电容一个接负,一个接正;CIN的两个电容一个接负,一个接正;

- (上图没有明确画出)断开GM2,CF由GM1的差分输出驱动;只是相当于放大零输入信号,没有进行放大。

- 之所以进行DAZ操作,是为了减少CHOP切换时瞬态的Glitch深度(个人理解,原文没有提)。此后要进行输入电容的切换,正向输入端PGA PreCharge Buffer需要给将电容上从VINN充到VINP;负向输入端PGA PreCharge Buffer需要给将电容上从VINP充到VINN。如此操作,输入电容先充了一半,CF电容也先充了一半。

D) CHOP2阶段:

- CIP的两个电容两个都接负;CIN的两个电容两个都接正;

- CF由GM1+GM2的差分输出驱动;

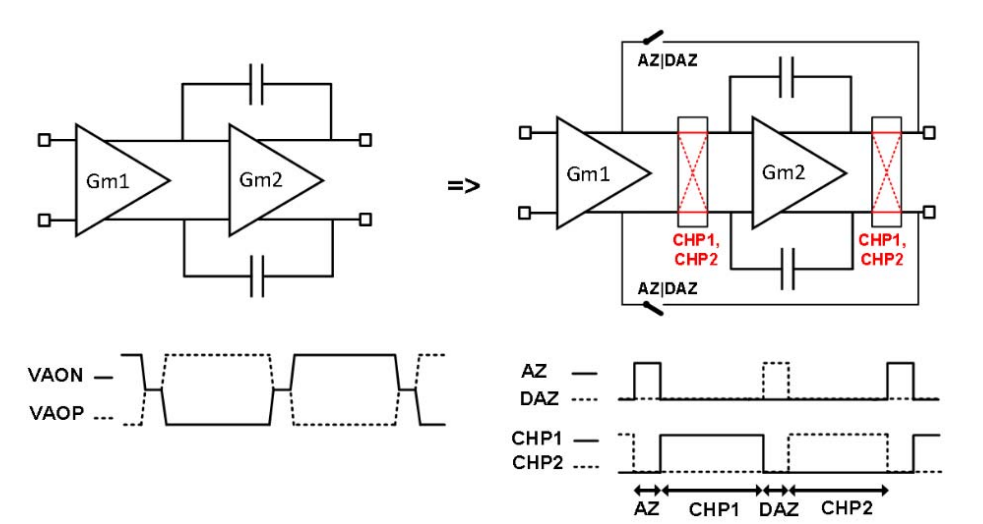

运放自身建立速度优化,只CHOP第一级:CCIA在Chop前后,意味着整个放大器都要完成VINN-VINP的切换,运放的速度受限于GBW以及gm/cc的slew速度。因此该运放只CHOP第一级folded cascode,不CHOP带米勒电容第二级class AB。

¶ 1.2 CHOP Ripple问题:AZ

在高增益下,为了抑制chopping导致的ripple,会采用

- DC SERVO LOOP (6,7)

- Ripple Reduction LOOP

- AZ & Chopping

相比电阻反馈的PGA,输入信号fully chopped,因此settling也更加有挑战,有CVF的电流。

¶ 1.3 PGA驱动问题:PreCharge & CHOP

CCIA的输入也是一个SC电路,也是存在2CVF的偏置电流。对于16KHz的CHOP频率以及4.48pF的输入电容,输入电流

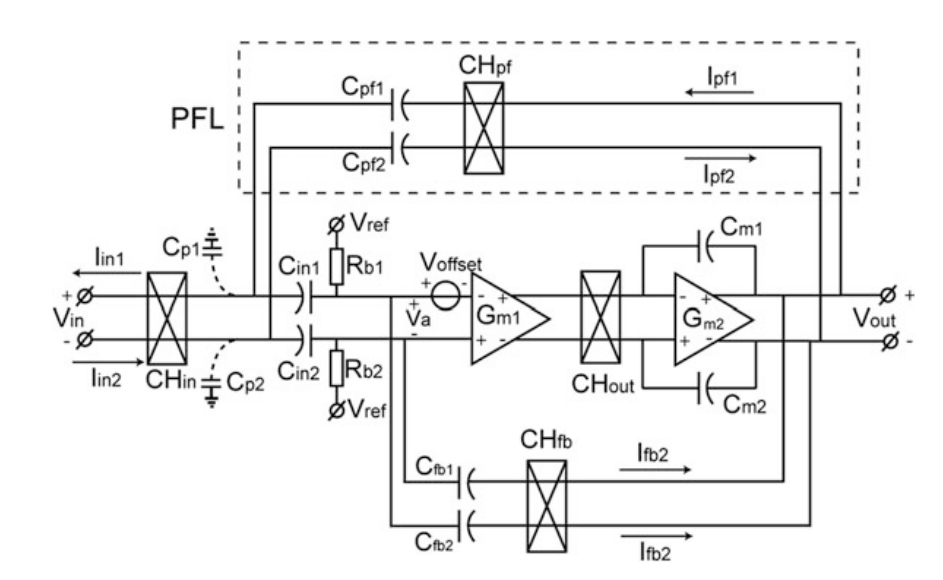

Positive Feedback Loop的方法,正向输入-正反馈电容-正向输出:Capacitively Coupled Chopper Instrumentation Amplifiers,page112

(1)仅能在G>1的前提下工作,当G=1时,正反馈电容上两个极板上的电压相同,Q=0,没有额外的电荷用于给CIN充电;

(2) 补偿能力受限于CPFL/CIN的匹配,其中CIN的真实电容需要加上输入寄生电容CP,这个CP是不确定的。

另一个解决办法就是Input Buffer,但是为了不让Input Buffer的非理想因素成为限制系统性能的瓶颈(系统的第的最前级Offset/Noise/INL等),这个Input Buffer通常只会做成PreCharge的形式,只在PGA CHOP开关发生切换时才工作,完成大信号的SLEW后,残余误差由外部信号源驱动。

输入偏置电流包含以下部分

(1)CHOP切换输入与输入电容的2CVF电流,这个电容指的是CCIA的CIN,或者是运放输入管栅极电容

(2)CHOP开关寄生电容,详见#输入电流分析

¶ 1.4 ADC驱动问题:PreCharge & DF

在这篇文章的作者说,AD7124-8,CS5530,ADS1282需要额外的ADC采样网络的输入Buffer,或者片外电容。

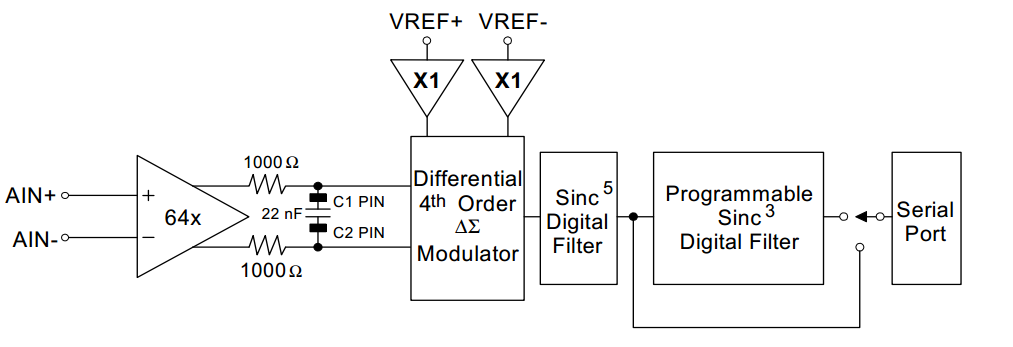

(1)ADI,AD7124,共模轨到轨放大器,框图上在PGA后面仍有Buffer

(2)Cirrus Logic,CS5530,固定64倍增益放大器,PGA差分输出跨接22nF电容

CS5530甚至给出了输入Buffer Pre-Charege导致的CVF模型

(3)TI,ADS1282,电阻反馈, 输入受限,either VINP or VINN,(GND+0.7, vdd-1.25),PGA差分输出跨接10nF电容

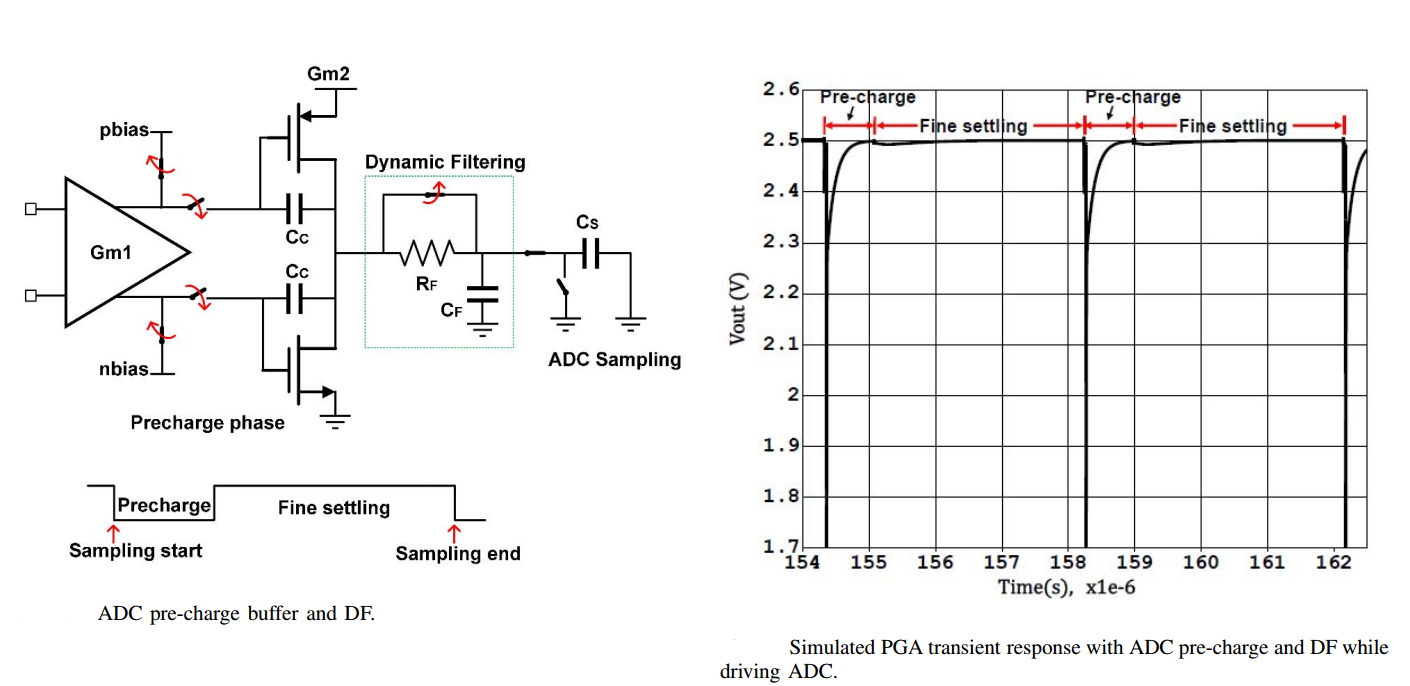

这篇论文的设计思路是,将输出级复用为PreCharge Buffer,同时也有一个在PreCharge时刻短路的RC Filter,称之为Dynamic Filter。文章说,20%的时间用于PreCharge,实现3mV的残余Offset,之后再用著放大器建立到5uV的精度。

计算一下单极点的settle对带宽的要求:

- 如果满摆幅输入,

- ADC的采样频率,建立时间只有一半,

- 放大器的带宽是,那么

那么BW导致的残差,该设计采样速率是(原文说是256K,但是后续计算计算没有乘以DutyCycle,因此猜想实际采样速率是128K,在Double Sampling下,采样速率是256K,拿256K去计算则无需考虑DutyCycle的问题)

- ,对应的残差为5uV

- ,对应的残差为5uV

实际上PGA的带宽要大于设计的带宽,同时为了抑制classAB输出级的噪声(因为前级对后级的噪声抑制前提是它有增益,高于GBW第一级就没有增益了,而输出级自身的带宽gm/CL为了保证稳定性通常是GBW的2~3倍),Dynamic Filter是必要的。在这篇论文中,R=20K,C=15pF,ADC的采样电容2pF,采样速度256KHz,大概估算一下

论文中的给出的结果是,如果没有DF,那么噪声大约是sqrt(1.6)=1.26倍。

¶ 2 设计细节

¶ 2.1 电路结构与开关时序

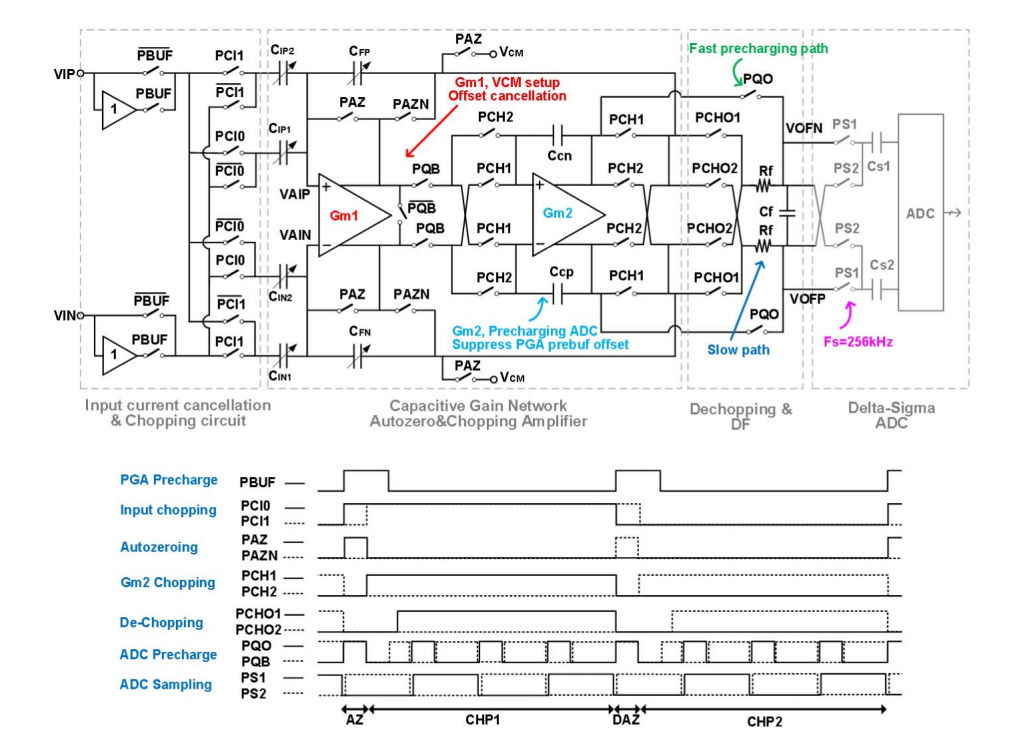

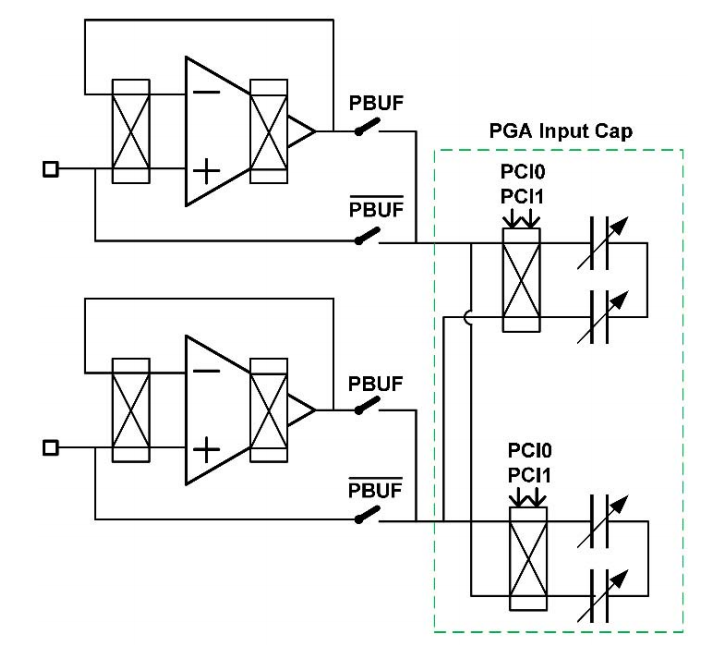

电路的框架如下:

大体理解这个电路:

(1)PCI0,PCI1是输入电容前的CHOP,与GM2后面的PCHO1/2完成了放大器的CHOP

(2)GM2前的PCH1/2,保证了GM2相对输入差分信号没有变化,因而CC上没有变化,避免SLEW。

(3) 但是GM2前PCH1/2改变整个反馈(CF)的极性,因而同时需要GM2后面的PCH1/2 De-Chop,之后再通过CF负反馈到放大器输入端。

(4) PQO是ADC PreCharge控制,发生在需要给ADC采样网络需要充电的时刻。对于Double Sampling,ADC PreCharge的频率是(ADC的采样频率,Double Sampling,意味着上升沿和下降沿同时采样,在输入端看见的采样频率是;如果是一次接VIN,一次接VCM,那么输入端看见的采样频率是,对于采样网络的驱动,无论何种采样方式,可用的建立时间都是)。

(5)PQB其实就是PQO的反向,在ADC PreCharge时刻,分为3种情况

- PGA正处于AZ状态,”CMFB电路“和”单位增益反馈“接管GM1的差分输出,同时断开与GM2的连接。

- PGA正处于放大状态,断开GM2后意味着断开了反馈环路,GM1工作在开环下会让输入饱和,因此让输出短路,避免输出饱和引起该节点电压的大范围Slew。

- PGA处于DAZ状态,GM1的差分输出,由GM1和CI/CF的电容反馈网络接管,同时断开与GM2的连接。

(6)PBUF是PGA preCharge控制,只会发生在AZ和DAZ时刻,只会发生在PGA CHOP切换时刻。

- PGA的输入接入Buffer时,必须将整个CI/CF的放大网络断开,因为CI/CF*OFS=128*10mV=1.28V的放大能力,很容易让输出饱和,引起输出端电压的大幅Slew。

- 为什么DAZ没有真的AZ是必要的,这是因为必须小于等于,这样才能将AZ的KT/C噪声CHOP走。在的情况下,每次KT/C噪声都经过了一正一负最后平均为零,从频域的角度看意味着KT/C噪声分布在的范围内,CHOP之后噪声的频率在

为了保证低频内看不到KT/C噪声的信号,则有

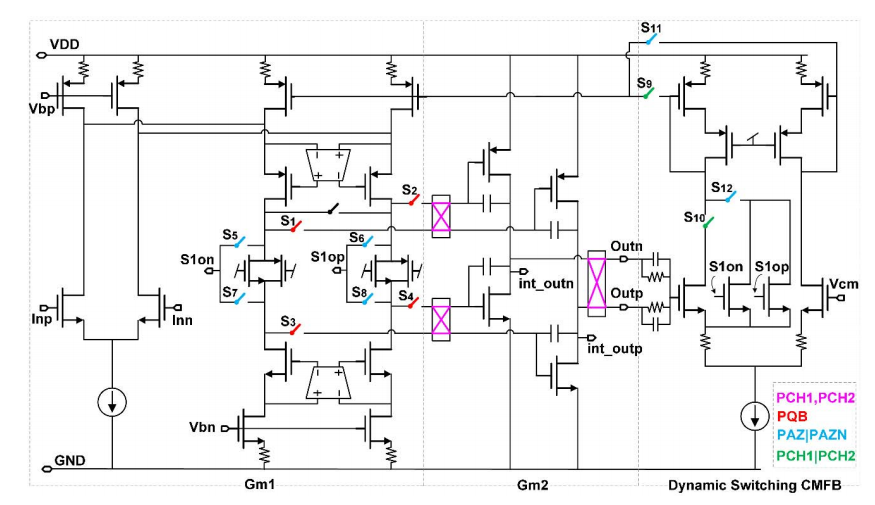

电路的详细设计如下:

¶ 2.2 增益配置

| Gain | 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 |

|---|---|---|---|---|---|---|---|---|

| CIN (pF) | 4.48 | 8.96 | 17.92 | 17.92 | 17.92 | 17.92 | 17.92 | 17.92 |

| CF | 4.48 | 4.48 | 4.48 | 2.24 | 1.12 | 0.56 | 0.28 | 0.14 |

¶ 2.3 设计结果

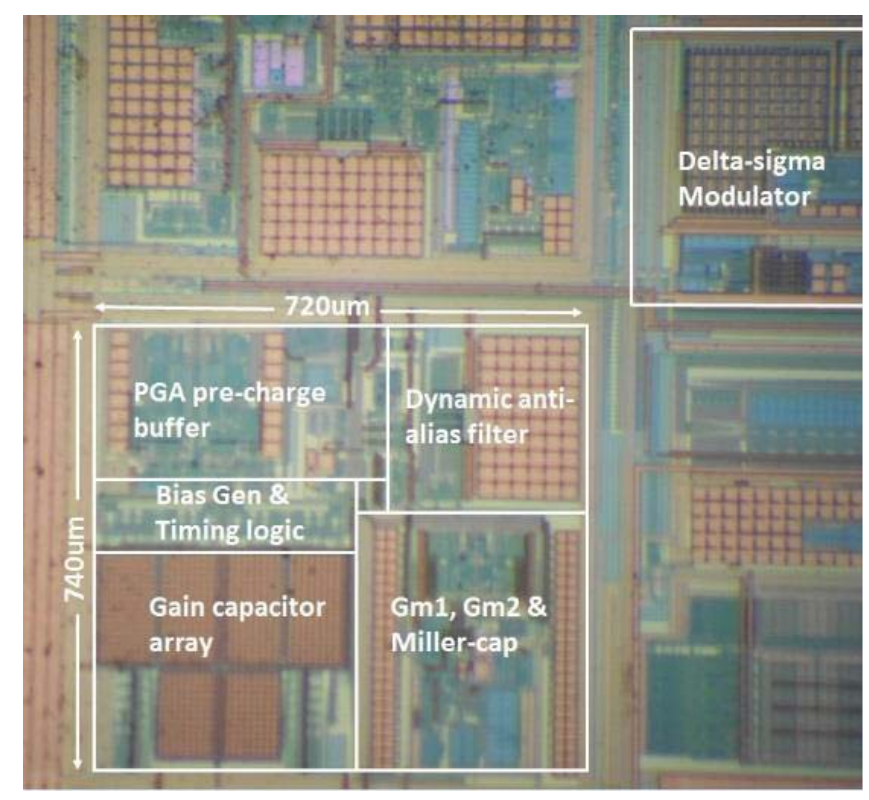

(1)Supply voltage 2.7~3.6, INL ±5ppm

(2) 65uA Main Amplifier, 45% Input Pair consum 30uA achieve gm of 430uS, input parasitic capacitor is 420fF, gm/Id=430/15? Drive fs=256KHz ADC (guess double sample, 128*2)

(3) Input buffer 10uA total of 2, 400pA input current, 16KHz PGA chopping frequency, 2uV offset

(4) Unity Gain Bandwidth 4MHz,gm/(2*pi*f)=17.11pF

(5) 0.18um CMOS Process, 0.53mm2

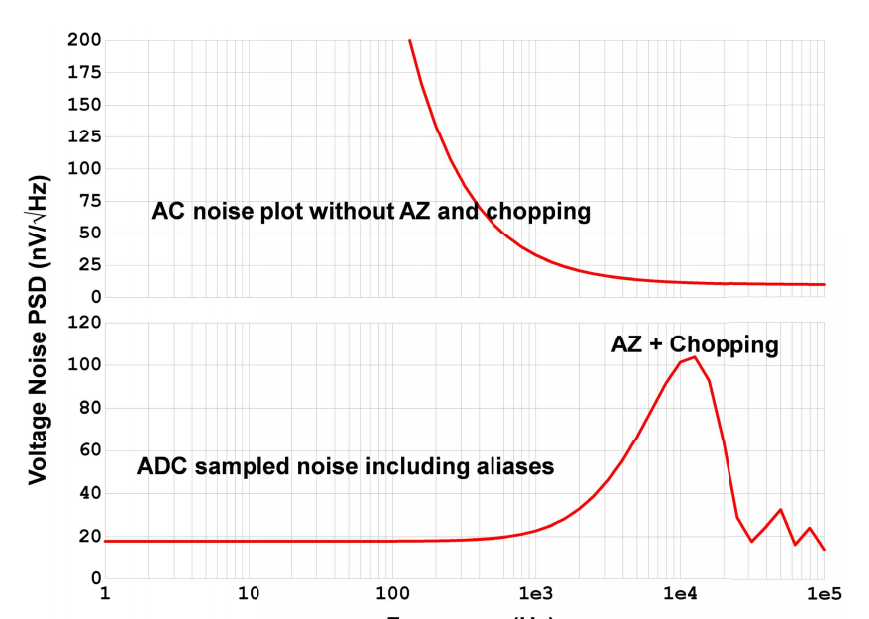

(6) AC input noise is 12nV/sqrt(Hz), alised noise is 19nV/sqrt(Hz)