Reference: Analog Circuit Design --- High-speed Clock and Data Recovery, High-performance Amplifiers, Power Management, Current Sense Amplifiers with Extended Common Mode Voltage Range

Chapter Download: Current_Sense_Amplifiers_with_Extended_Common_Mode_Voltage_Range.pdf

¶ Current Sense Amplifier Definition

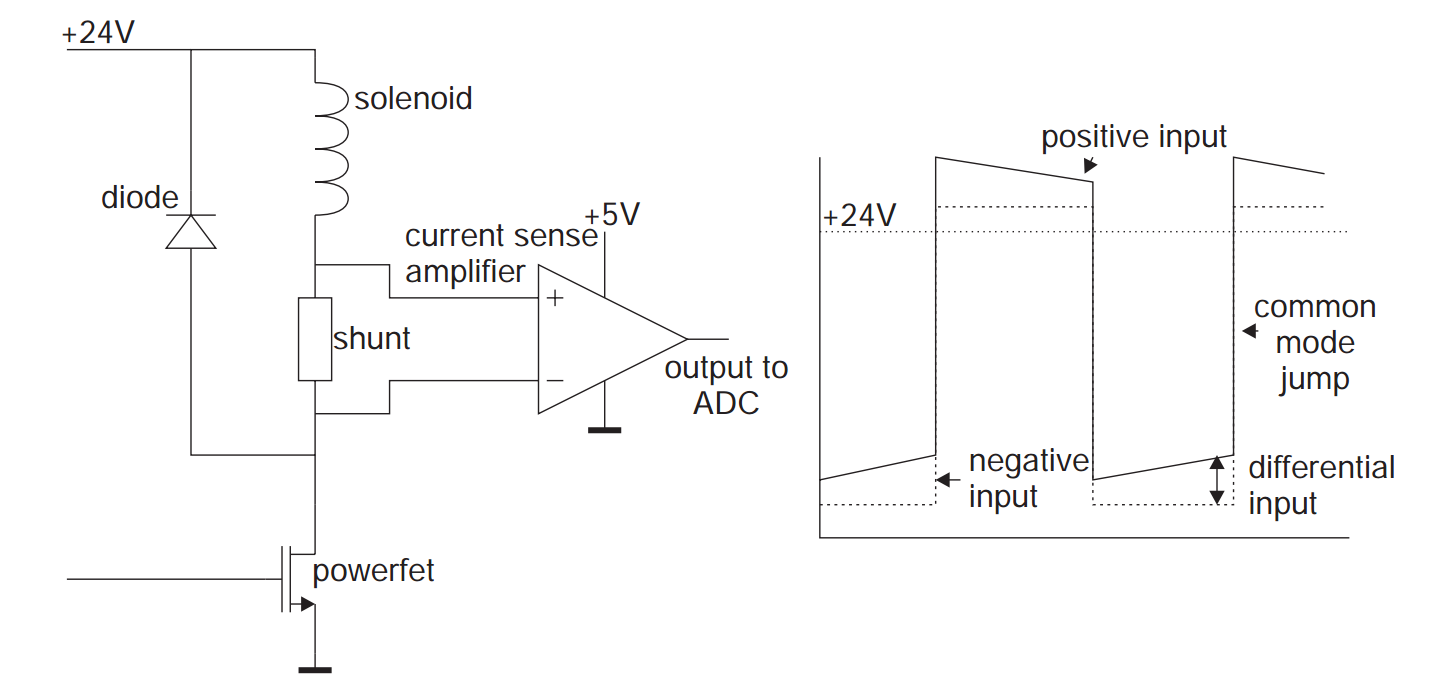

电流放大器,其实并非是电流输入,而是侧量 shunt resistor 上的 difference voltage 的放大器,只是实则个 shunt resistor 上的 common mode voltage 的范围很大,超过了电源轨,而且可能有非常快速的共模变化。一个典型应用场景如下,POWERFET 控制一个线圈的系统中,通过 shunt 电阻测量流过线圈的电流,共模电压大范围跳变,差模相对较小。

¶ Current Sense Amplifiers in Low-Voltage Fabrication Processes

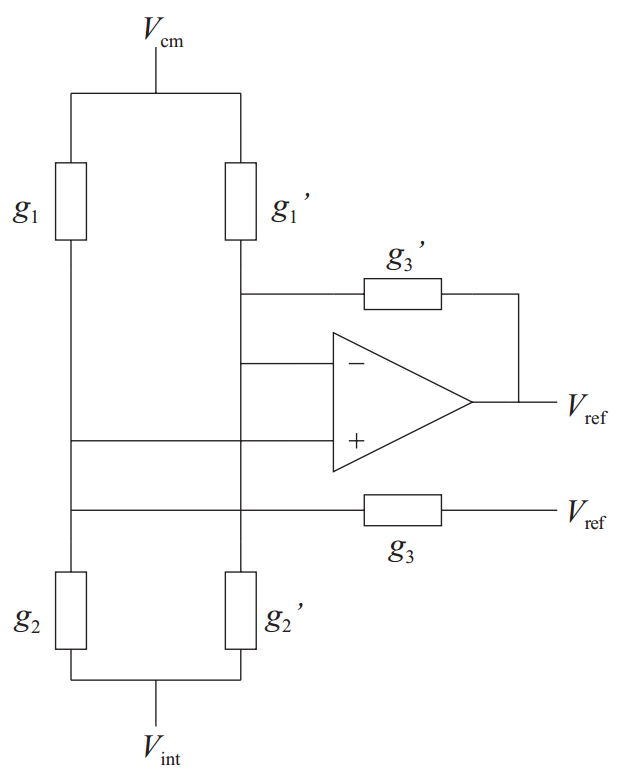

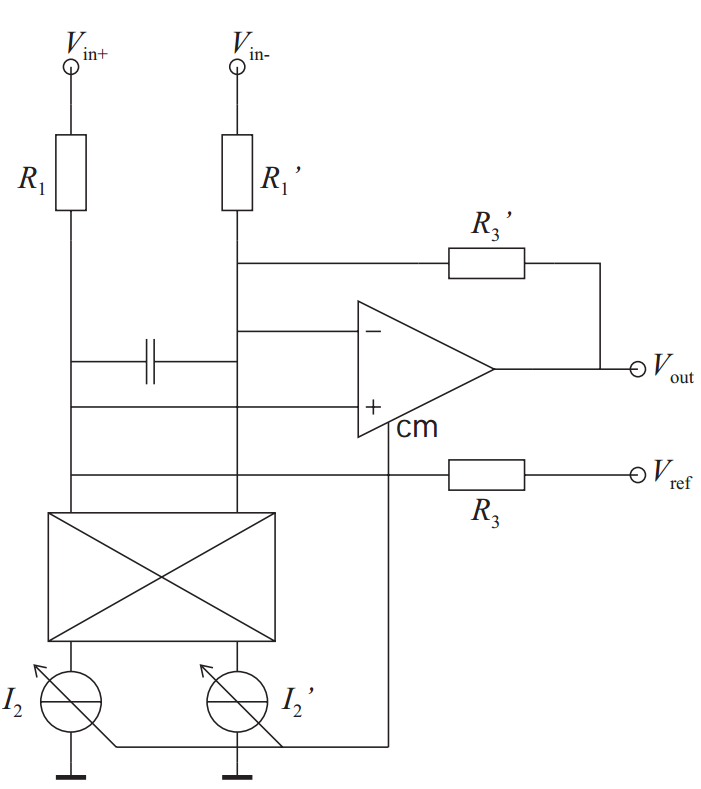

使用低压工艺去做这样一个放大器,通常的做法是使用电桥,主要目的是利用R1/R2的分压,实现共模向GND的偏移。在本章接下来的分析中,可以看到这样做是有代价的, 会导致失调和噪声增大、速度降低的问题,并且由于电阻桥的匹配问题也会引起CMRR的恶化

增益与共模衰减

如果认为输入分别是 ,在反馈作用下放大器的输入端虚短电压为 那么则有如下方程

求解 和 可以得到

取小一点让放大器输入端电压更接近 而非 , 决定增益所以 需要大一点,因此有 ;

放大器失调

¶ CM Voltage Divider Using Bridge

假设放大器正向输入端有一个等效 那么等效输入失调如下,这要求 尽可能大和 尽可能大一点,并联的缘故最后是取决于 , 取大值与我们之前降低放大器输入共模的初衷相悖;因为,所以这里真正 Dominant 是

ClearAll["Global`*"]

vin = 0;

vgnd = 0;

vref = 0;

vcmap = vcma - vos/2;

vcman = vcma + vos/2;

eq1 = (vcm + vin/2 - vcmap)/r1 + (vgnd - vcmap)/r2 + (vref - vcmap)/r3 == 0;

eq2 = (vcm - vin/2 - vcman)/r1 + (vgnd - vcman)/r2 + (vout - vcman)/r3 == 0;

ans = Solve[{eq1, eq2}, {vout, vcma}]

ans[[1, 1, 2]]/(r3/r1) // FullSimplify // ExpandAll

电阻噪声

在输入端的等效噪声功率,6个电阻的等效输入噪声,可以按照如下公式,轻松计算得到

注:原文的计算应该有误,非相关噪声是平方求和的关系,且功率在计算增益时也是平方的关系;因为,所以这里真正 Dominant 是

增益带宽积

这里只需要计算下反馈系数即可,增益为 ,反馈系数是通过 反馈到 上去,因此如果假设 OPA 自身的 Unity Gain-Bandwidth 为 的话,那么在电阻网络下的增益带宽积如下

如果没有额外 的影响(),在高增益情况下 ,主极点位置是基本不变的。但是如果此时并联的 拉低了等效 的阻抗,就会让带宽降低。

电阻匹配

The effect of resistor mismatch in the dynamic bridge circuit can be analyzed using the circuit shown below.

One can calculate the input offset voltage required to counterbalance the effect of resistor mismatch, assuming that the input is biased at a common mode voltage the output and the reference input are both fixed at an output reference voltage and the input common mode divider resistors are biased at an internal reference voltage .

文章中这样的表达式写得很漂亮,然而不算特别直观,我们按照 的数值进行化简,抽取主要矛盾后观察到关键点就是 和 的精度

Sensing Both Positive and Negative VCM:下图所示的方案,通过将放大器输入共模反向放大到 VDD/GND,目的是改变R2电阻下方的偏置电位,从而同时兼容正负高压共模

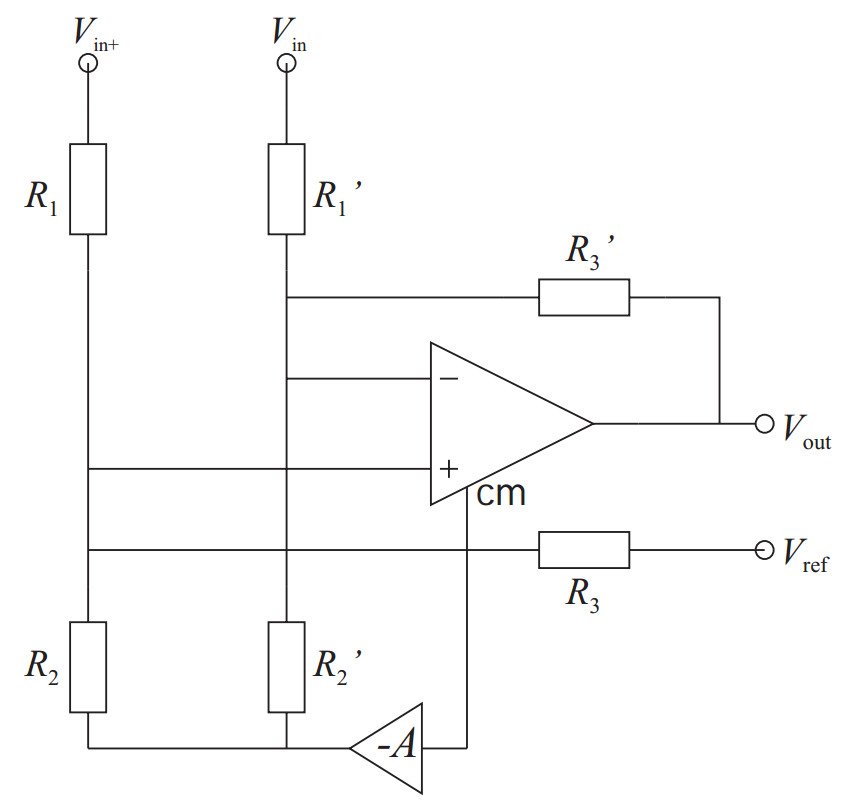

¶ IR Level Shift using VCCS

Bridge Divider 由于 R2 导致环路反馈系数低于增益倒数,从而导致系统 Noise/Offset/Gain-Bandwidth 被恶化。除此之外,R2本身的噪声以及失配带来的 CMRR 恶化也是问题。

将低阻值的 R2 替换为 CM-Voltage-Control-Current-Source,实现了 R2 的高阻,这样避免了前者的问题; 共源/共射的电流镜其低频噪声在相同电流下更大,且失配更高,使用 Source Degeneration 可以优化噪声和失配(右图);但是实际上这需要更低阻值R2,这是因为如果要让放大器输入端看到的电压在VDD以内,所需要的电流和之前一样,然而给R2的空间却不多了,R2=(VDD-VCE)/I,这样 4kT/R2 的噪声电流还是会注入到输入电阻R1上;除此之外 Q2 的 VBE 的电压失配除以 R2 产生的失配电流,和噪声电流一样还是会注入到R1上;

这里或许噪声不是主要矛盾,重点解决 Offset 的问题,通过受控电流源将 offset 的矛盾转移到了电流镜上,在电流镜这里使用 Chopping 方式处理 Offset 问题(见专利US6819170.pdf),Chopping 的频率高于 Signal Path 的频率,在输入端引入 Capacitor ,在进入放大器之前就将 Chopping Glitch 给滤掉。

这样实现的 100~300 uV 的失调,10uV/°C 的 Offset-TC,100dB CMRR,1uV/sqrt(Hz) 的噪声

¶ Current Sense Amplifiers in High-Voltage Fabrication Processes

¶ Common-Base-Input-Stage

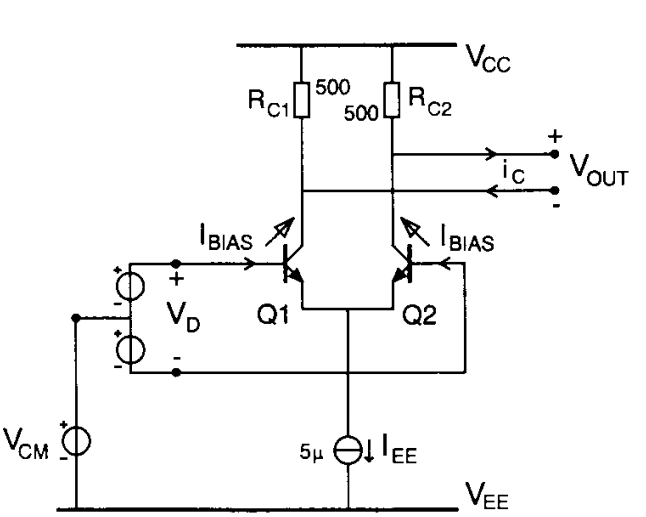

这一小节整理了 1994 年 Huijsing 的这篇论文用 Common-Base-Stage 去解决超电源轨输入共模的 “心路历程”。

在BJT管作为输入级的放大器设计中,如果共模电压超出电源,会导致输入电流提高以及 signal reversal,简单说就是 BC Junction 正偏,输入电流提高还是小问题,但是 signal reversal 会让环路反馈极性变化,系统就直接挂掉了,所以需要扩展共模输入范围。

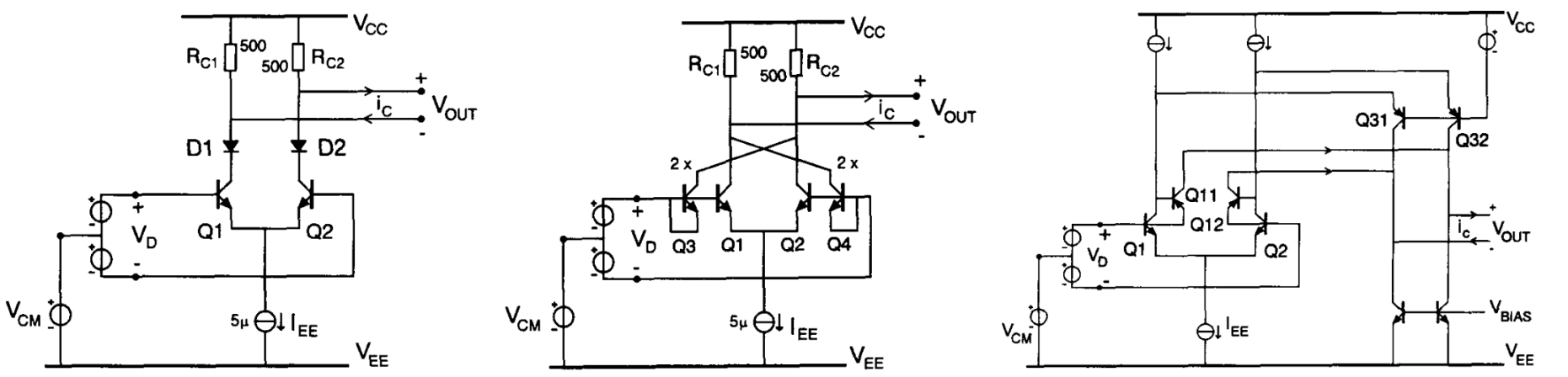

解决思路如下,

- 左图:通过增加 D1/D2 防止电流倒灌。这不是实现 CMVR 扩展的问题,而是处理意外CM超压问题的保护机制;但是 Diode 压降会压缩输入输出范围。

- 中图:Overcompensation,顾名思义,如果 Q1/Q2 发生了 BC 正偏,D3/D4 也会由反偏进入正偏,Cross Connection下,注入2倍相反极性的电流。同样这也是CM超压的保护机制,不是用来真正扩展CMVR的,因为CM高于VDD-0.7V 后,gm 是会变化的,随着共模提高 gm 也会提高,这同样会导致稳定性问题;显然输入电流也会提高。

- 右图:另一种 Overcompensation,Q11/Q12 这个 lateral PNP 的 EB PN 结 可以和 输入管的 Vertical-NPN 的 BC PN 结匹配,在Q12的 EB PN 结的跟随导通作用下,Q2 就永远不会反偏。Q11/Q12的电流,还是以相反的方向注入到输出级。同理,CM 超压后输入电流还是会提高,而且gm 也会变化。

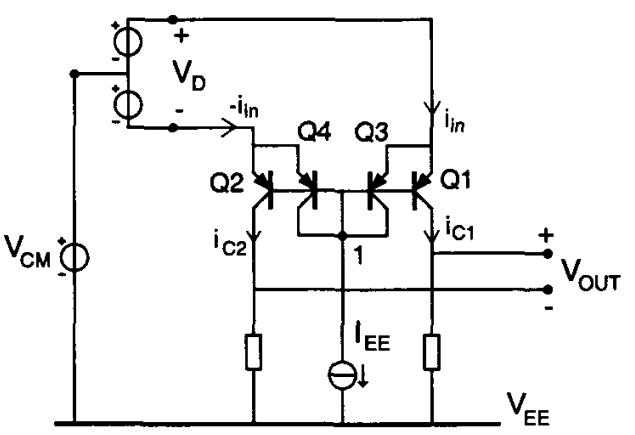

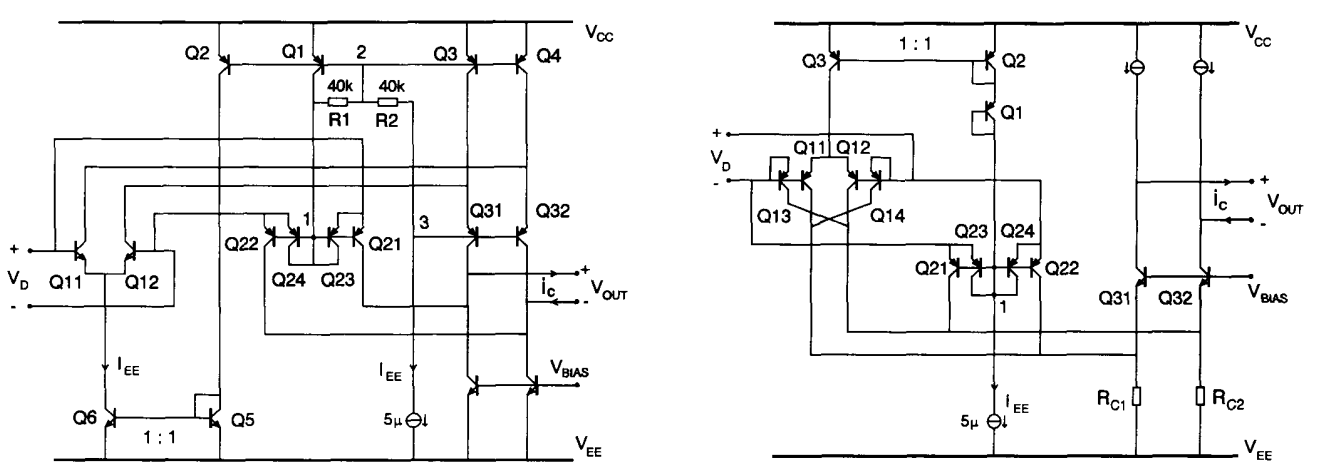

Gert van der Horn 提出的解决思路如下,Q3/Q4 是在 IEEE 作用下产生偏置电压,输入管 Q2/Q1 会镜像 IEE 的电流,这样保证了在不同 VCM 下输入级电流是一致的,能这样做的前提是 Q1/Q2/Q3/Q4 的 BC 结能搞抗高压;

具体的实施方案如下,左图是 NPN 输入级 +PNP 的 CB-Extension,低共模电压情况下,Diode 5uA 电流下 Vnode2=VCC-0.4V,在5uA作用下 Vnode1=VCC-0.4V,Vnode3=VCC-0.6V,此时只有 Q11/Q12 在工作。单输入共模电压超过 VCC+0.2V 后,Q23/Q24 导通,5uA的IEE 不在由Diode Q1 提供,而实由 Q23/Q24 Emitter-Base Diode 提供,这样主 NPN Q11/Q12 输入级不再工作,而是由 Q21/Q22 去工作;

右图是 PNP 输入级 + PNP 的 CB-Extension,思路一致,在工艺受限的年代,Vertical-NPN 不如 Lateral-PNP 的 BE 结去承受高压。比较器工作条件下,Diffential 电压很大,那么 NPN 的 VBE 不足以承受 Vdiff/2 的电压

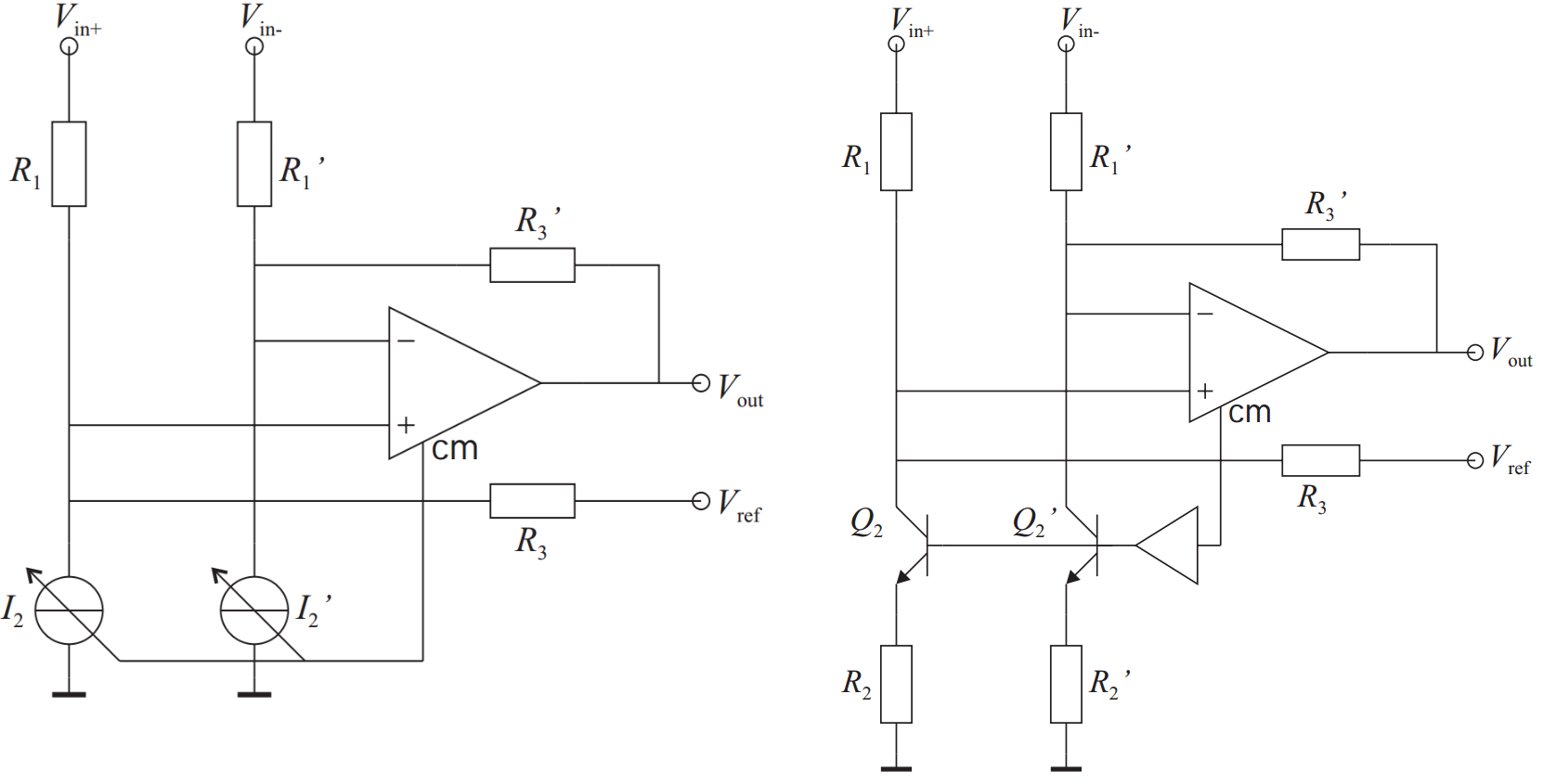

¶ Simple Current Amplifier using CB

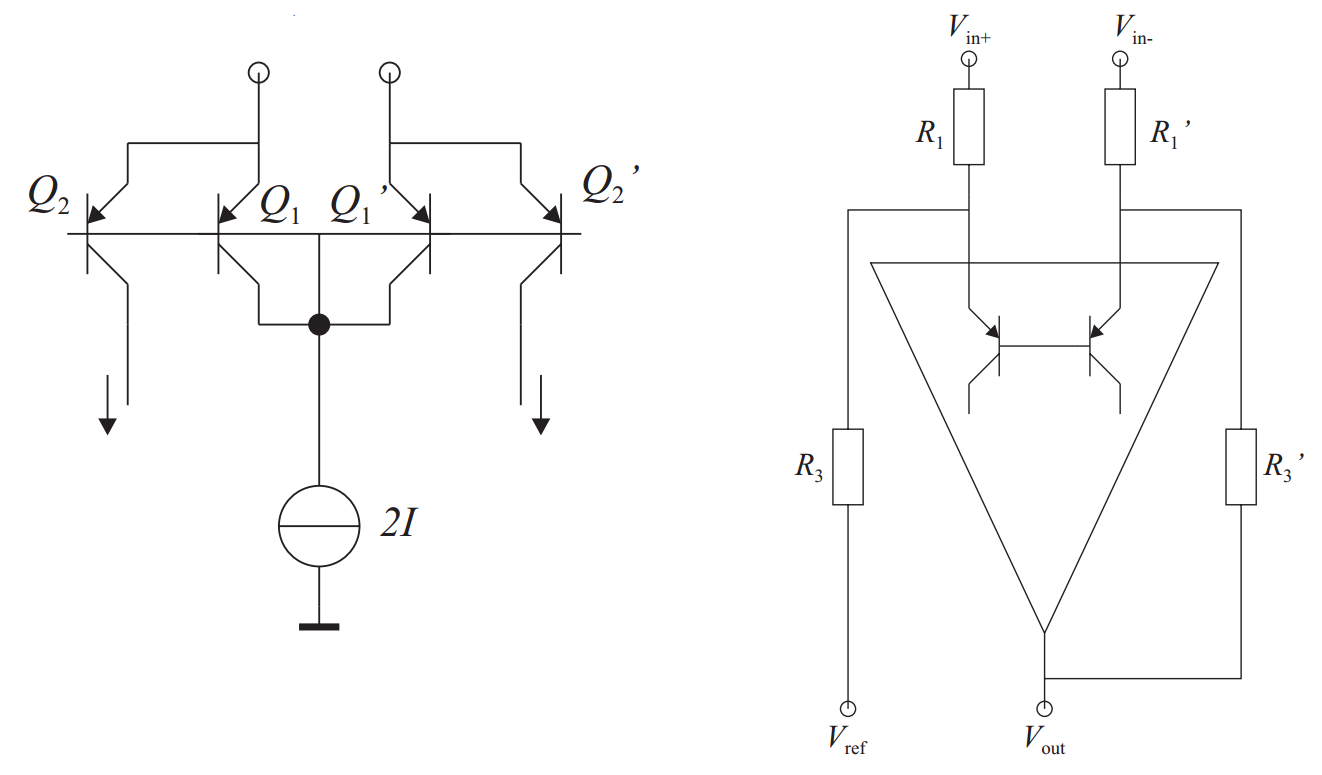

利用 Common Base 输入级(左图)实现高压输入,低压输出后,就可以带上电阻网络(右图)实现 HV-Current Amplifier 了,该电路的主要问题是输出与输入通过电阻网络耦合在一起,CMRR做不高

¶ VI-Converter using Gain Boosting

首先将差分输入信号转换为电流,然后让电流基于 REF/GND 产生输出电压,就可以实现输入与输出共模的隔离,从而提高 CMRR。

- 左图是 Gain Boosting 的方式去实现,在放大器 Gain Boosting 的作用下,MP1的 Source 端电压一致,这样差分电流就精确等于 Vdiff/R1,放大器可以由输入 Vin+ 供电,负电源轨可以通过 Zener 管产生一个各 Vin+ - Vzener 的电压;

- 右图是一个简单优雅的电路具体实现,Gain Boosting 放大器的 Source 通过 R2/R2‘ 分压产生共模,也是一个低压器件实现 Gain Boosting 的实现方案

¶ Current Feedback

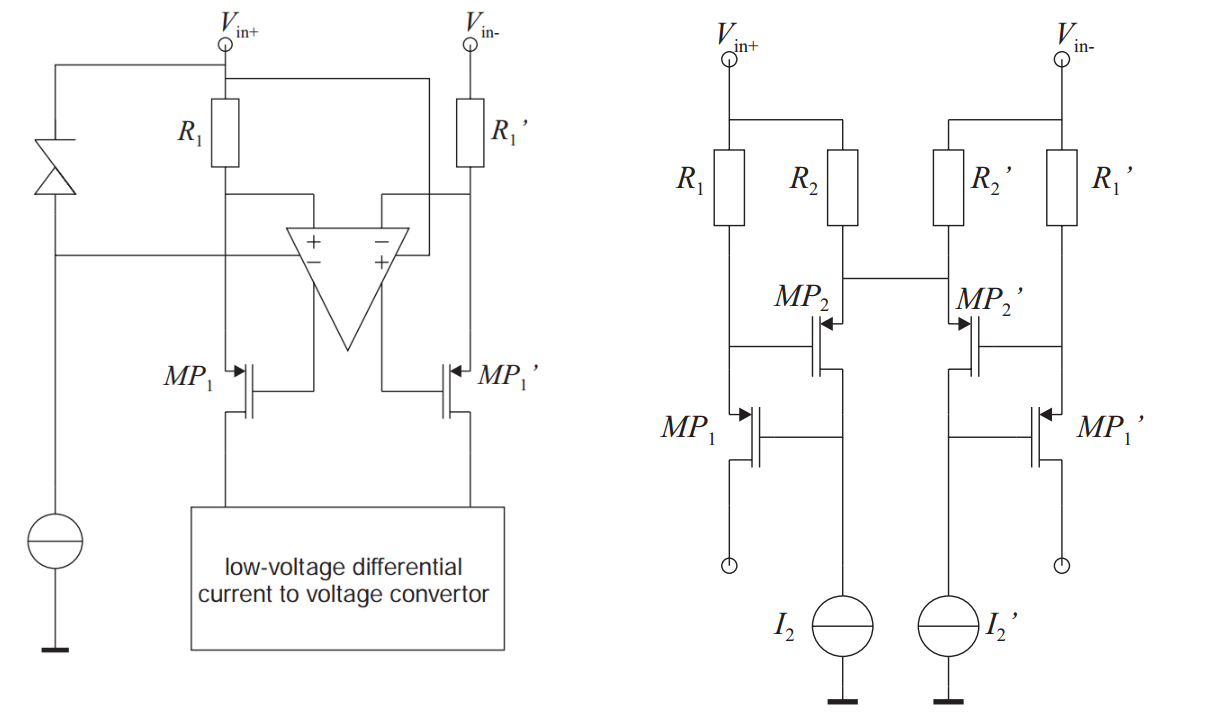

如下图所示,另外一种方式不在针对MP1去做 Gain Boosting,而是将 MP1,放大器,甚至输出管 MN3 都纳入到整个 feedback Loop 当中,这样同样实现了 MP1 Source 电位的一致,实现差分电流精准等于 Vdiff/R1 的效果,并最终通过 MN3 流向电阻 R3 上产生输出电压。

原文没有分析优缺点,以下是笔者拙见:

- 将整个信号通路都纳入到反馈环路可以实现更高的增益,从而实现更精准的 VI Conversion;

- 高压处理逻辑相对简单,VI-Converter using Gain Boosting 中的放大器供电或者自偏在启动过程或者共模变化过程中还是有待商榷的;

- 共模仍然是隔离的,只是通过 MN3 的有限输出阻抗 1/gds3 仍然有馈通通路;

- 初看I1的失配问题需要注意。

右图是一个具体单端输出的电路实现,简单高效

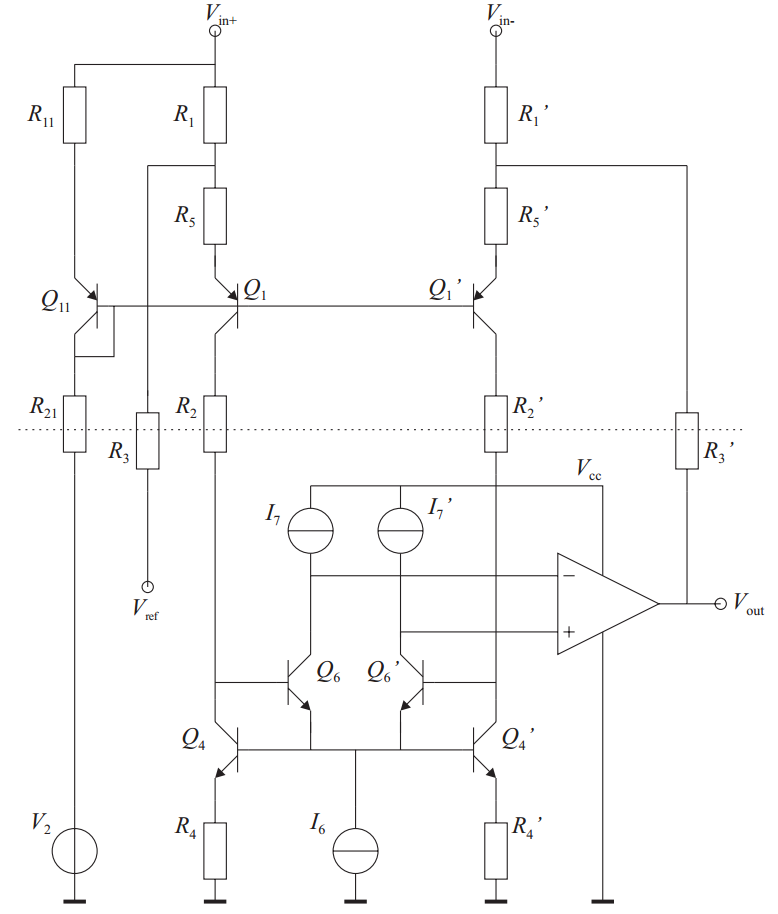

¶ HV Current Amplifier in SOI Process

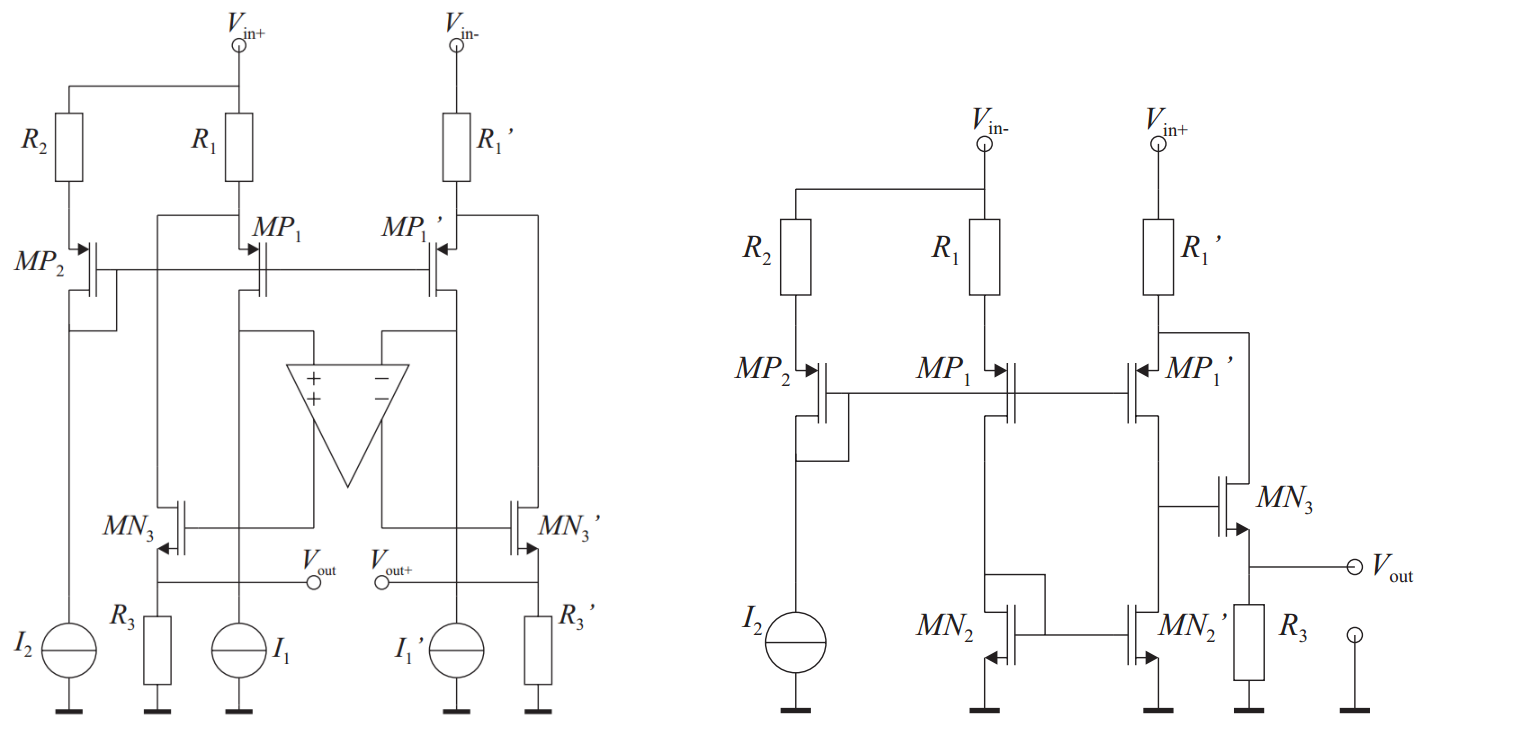

下面这个结构,不使用 HV 工艺,但是使用 SOI (Silicon on Insulator) 工艺,在SOI 工艺下,衬底完全隔离,不受限于衬底偏差高压的问题,因此只要管子自己的电压自洽,是不必理会其它区域的管子的电压状态的。比如如下电路,Q11/Q1/Q1‘工作在 65V~60V 这个区间,Q4/Q4'工作在 5V~0V,互不影响

电路分析如下:

- 整体上,是一个 Resistive Feedback 的电路,增益就是 R3/R1,因此 CMRR 会成为瓶颈;

- R2/R2’ 上面的 IR-Drop 承担了 Leveshift,隔离高低压的作用,方式是通过左侧的 R11/Q11/R21/V2 通路,将 R2 Bottom 的电压钳位在 V2;

- R2 Bottom 这个点,上面是 floating Current,下面得是个低阻才能实现电压钳位的效果,不然上下都是 Current Source 高阻,其电压是确定不下来的,这个电路非常巧妙的一点是 利用 Q6/Q6‘ 让 Q4/Q4' 的 Collector 在共模电压下看起来仍然是一个 Diode,但是在差模下看起来仍然是 Current Mirror,当然了这就是通过 Mirror 实现 CMFB 的通用效果/机制;

- 放大器的第二级是Q6/I7构成的,第三级是一个放大器,整体上这是一个三级放大器;

- 这个电路存在的问题是 Q11/Q1/Q1' 的浮空电流源/电流镜的偏置电路,是随着输入电流变化的,这导致输入管Q1的 gm 在变化,这对三级放大器的稳定性补偿是不可接受的的,因此使用了 Source Degeneration Resistor R5 去让输入级的 gm 恒等于 1/R5。

这个电路可以在5V供电下实现 CMVR 3V~60V, 初始精度并不不好,TRIM后可以实现 100dB 的 CMRR 以及小于 100uV 的 Offset。